Technological University Dublin ARROW@TU Dublin

Doctoral

Engineering

2013-8

# Grid Voltage Unbalance and The Integration of DFIG's

Joseph Kearney Technological University Dublin, joseph.kearney@tudublin.ie

Follow this and additional works at: https://arrow.tudublin.ie/engdoc

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Kearney, J. (2013) *Grid Voltage Unbalance and The Integration of DFIG's.* Doctoral Thesis, Technological University Dublin. doi:10.21427/D7QK6V

This Theses, Ph.D is brought to you for free and open access by the Engineering at ARROW@TU Dublin. It has been accepted for inclusion in Doctoral by an authorized administrator of ARROW@TU Dublin. For more information, please contact arrow.admin@tudublin.ie, aisling.coyne@tudublin.ie, vera.kilshaw@tudublin.ie.

# Grid Voltage Unbalance and The Integration of DFIG's

Joseph Kearney, M.Eng.

# A thesis submitted for the degree of Doctor of Philosophy to the Dublin Institute of Technology

Supervised by Prof. Eugene Coyle and Dr. Michael Conlon

School of Electrical and Electronic Engineering Dublin Institute of Technology Kevin Street

Dublin 8

August 2013

#### **DEDICATED TO**

#### **MY MOTHER**

## MY WIFE

#### AND

## **MY DAUGHTER**

J Kearney PhD Thesis

#### Abstract

Double-fed induction generators (DFIG's) became the predominant generator installed for wind generation applications in the mid 1990's. Issues pertaining to the operation and control of DFIG's subsequently became apparent, particularly in weak areas of the grid network. Ironically weak areas of the grid tend to be where the average wind speed is high and the usual location of wind farms. One of the issues that emerged was the quality of the voltage in the network at the point of common coupling (PCC) with the DFIG's. An important issue is the question of voltage unbalance at the PCC.

As part of this work, research was undertaken into the issue of voltage unbalance in a distribution network. Investigative studies were undertaken on a small wind farm connected to the Irish distribution network. The results obtained were then analysed and conclusions drawn, with recording of daily, weekly and seasonal variation of voltage unbalance. The behaviour of DFIG's to varying levels of network voltage unbalance at the wind farm was analysed, and it was observed that the DFIG's had difficulty remaining connected to the distribution network when voltage unbalance exceeded certain threshold levels.

The behaviour of DFIG's to the effects of grid network voltage unbalance is further investigated in this work. A literature review was undertaken of the effects that utility network voltage unbalance has on DFIG's. Emerging from this research, the suitability of appropriate control schemes to alleviate the problems caused by grid voltage unbalance were investigated. Control techniques to improve performance of a DFIG during conditions of asymmetrical grid voltage including measures to control the rotorside and grid-side converters in a DFIG, were designed and then implemented in

Matlab/Simulink and results showed improved behaviour. A synchronous generator system was similarly investigated and improvements shown.

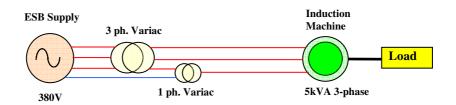

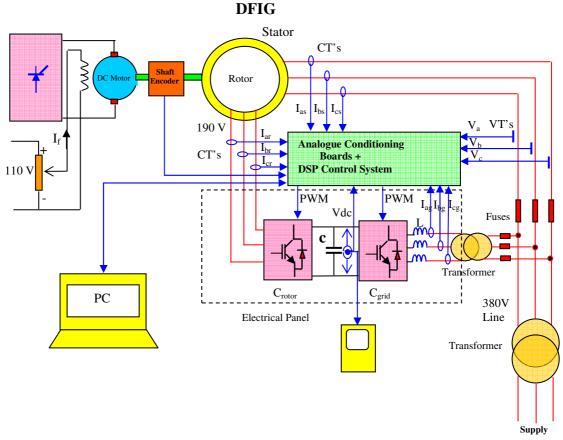

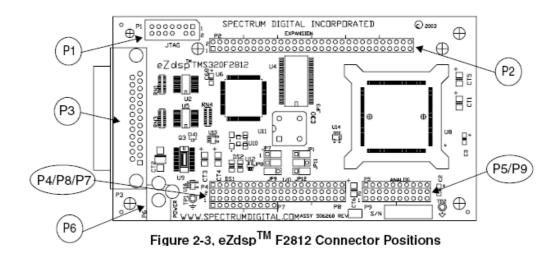

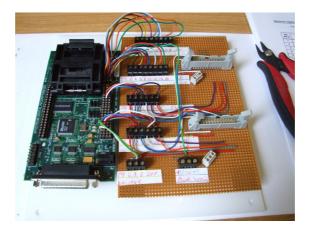

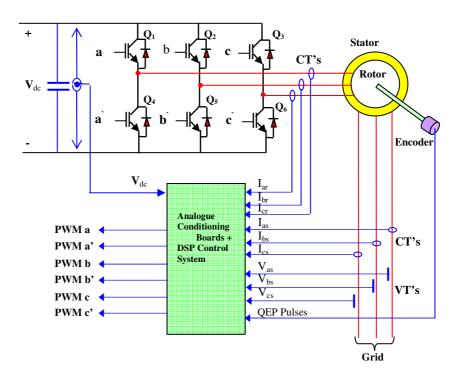

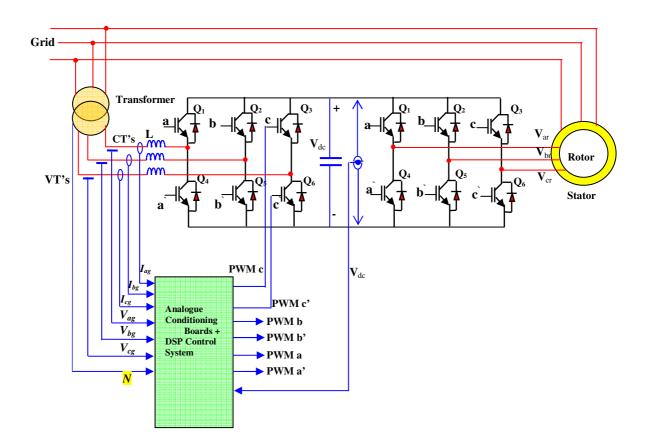

This research also includes development of a laboratory based DFIG test system. A DSP based digital microcontroller and interfacing hardware has been developed for a 5kVA DFIG laboratory based system. The system comprises of a machine set; a dc machine with common shaft coupling to a three-phase wound rotor induction machine. The dc machine emulates a wind turbine, and drives the induction machine in response to required speed. A converter has been constructed to control the rotor power of the induction machine. Interfacing schemes for the required feedback signals including voltage and current transducers and speed measurement were designed to enable control of both the rotor-side and grid-side converters of the DFIG. Grid/stator voltage oriented control is implemented to control both the rotor side and grid side converters respectively. An additional feature is the implementation of a single DSP controller, configured to control both the rotor side and grid side converters simultaneously.

Initially the DFIG test rig was tested as a standalone system, with a load bank connected to the stator terminals of the induction machine. Testing of the DFIG was also conducted with the test rig connected directly to the grid, and the system operated in subsynchronous and super-synchronous modes of operation.

Hardware and software solutions were implemented to reasonable success. The laboratory based test rig has been designed for operation as a rotor converter for a DFIG; however the converter can also be configured to operate as a system for a synchronous generator, or for operation as a machine drive. Further research may allow the rig to be used as a DFIG/UPQC (unified power quality controller) test bed.

J Kearney PhD Thesis

iv

## Declaration

I certify that this thesis which I now submit for examination for the award of Doctor of Philosophy, is entirely my own work and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

This thesis was prepared according to the regulations for post graduate study by research of the Dublin Institute of Technology and has not been submitted in whole or part for an award in any other Institute or University.

The work reported on in this thesis conforms to the principles and requirements of the Institute's guidelines for ethics in research.

The Institute has permission to keep, to lend or to copy this thesis in whole or in part, on condition that any such use of the material of the thesis be duly acknowledged.

Signature \_\_\_\_\_ Date \_\_\_\_ Date \_\_\_\_ 8/8/2013\_\_\_\_\_

Candidate

#### Acknowledgements

I would like to thank my project supervisors Dr. Michael Conlon for his help and support and Prof. Eugene Coyle for his loyalty, patience and understanding. Sincere thanks to Terry Kelly for his assistance with the test rig and all matters concerning the Electrical Energy Laboratory. I would also like to thank my office colleagues Dr. Richard Hayes and Kevin Sullivan for their support. And many thanks to friends John and Aideen for all their good wishes and moral support.

Most especially I most sincerely thank my wife and daughter for their support, patience, forbearance and love throughout the work involved in the preparation of this thesis. And also a very special thanks to my mother who always encouraged and supported me.

J Kearney PhD Thesis

# List of Abbreviations

| ABS   | Absolute Value                               |

|-------|----------------------------------------------|

| AC    | Alternating Current                          |

| ADC   | Analogue to Digital Converter                |

| CSI   | Current Source Inverter                      |

| CSS   | Code Composer Studio                         |

| DAC   | Digital to Analogue Converter                |

| DC    | Direct Current                               |

| DSO   | Distribution System Operator                 |

| DFIG  | Doubly-fed Induction Generator               |

| DG    | Distributed Generation                       |

| DSP   | Digital Signal Processor                     |

| DTC   | Direct Torque Control                        |

| EOC   | End of Conversion                            |

| EU    | European Union                               |

| EVA,B | Event Manager A, B                           |

| FOC   | Field Oriented Control                       |

| FRT   | Fault Ride Through                           |

| FSIG  | Fixed Speed Induction Generator              |

| IGBT  | Insulated Gate Bipolar Transistor            |

| IG    | Induction Generator                          |

| IM    | Induction Machine                            |

| ISR   | Interrupt Service Routine                    |

| MIPS  | Million Instructions Per second              |

| PCC   | Point of Common Coupling                     |

| PCB   | Printed Circuit Board                        |

| p.u.  | Per Unit (i.e. referred to normalised value) |

| PQ    | Power Quality                                |

| PWM   | Pulse Width Modulation                       |

| PI    | Proportional Integral controller             |

| PLL   | Phase Locked Loop                            |

| SCIG  | Squirrel Cage Induction Generator            |

| SOC   | Start of Conversion                          |

| SFO   | Stator Flux Oriented Control                 |

|       |                                              |

| SVC  | Static VAR Compensator            |

|------|-----------------------------------|

| SVM  | Space Vector Modulation           |

| SVO  | Stator Voltage Oriented Control   |

| THD  | Total Harmonic Distortion         |

| THDv | Total Harmonic Voltage Distortion |

| THDi | Total Harmonic Current Distortion |

| TI   | Texas Instruments                 |

| TSO  | Transmission System Operator      |

| UPS  | Uninterruptible Power Supply      |

| VSI  | Voltage Source Inverter           |

| WECS | Wind Energy Conversion Systems    |

| WFPS | Wind Farm Power Stations          |

| CWFS | Contiguous Wind Farm Site         |

| TR   | Transformer                       |

J Kearney PhD Thesis

## Contents

| 2.2 Potential problems associated with connection to g rid   |

|--------------------------------------------------------------|

| 2.1.3 Voltage Sags/Dips                                      |

| 2.1.2 Power Quality of Wind Turbines                         |

| 2.1 Introduction to Power Quality                            |

| CHAPTER 2 VOLTAGE UNBALANCE LITERATURE REVIEW                |

| 1.5 Thesis of gamsation                                      |

| 1.3 Thesis Organisation                                      |

| The work in this thesis focuses on the following objectives: |

| 1.2 Research objectives                                      |

| 1.1 Introduction                                             |

| CHAPTER 1 INTRODUCTION                                       |

| LIST OF SYMBOLS                                              |

|                                                              |

| GENERAL CONVENTIONS                                          |

| LIST OF FIGURES                                              |

| CONTENTS 1                                                   |

| LIST OF ABBREVIATIONS VII                                    |

| ACKNOWLEDGEMENTS VI                                          |

| DECLARATIONV                                                 |

| ABSTRACT III                                                 |

|                                                              |

| 2.3  | Inte   | egration of Wind Energy in National Grids         |    |

|------|--------|---------------------------------------------------|----|

|      | 2.3.1  | Connection Requirements of Wind Turbines          | 34 |

|      | 2.3.2  | Voltage Drop Ride-through Requirements            | 35 |

|      | 2.3.3  | Distribution System in Ireland                    | 36 |

| 2.4  | Vol    | tage Unbalance                                    |    |

| 2.5  | Vol    | tage Measurement and Voltage Unbalance Standards  | 39 |

| 2.7  | Vol    | tage Unbalance Sags/Dips – Types                  | 43 |

| 2.8  | Vol    | tage Unbalance Behaviour of Induction Machines    | 44 |

| 2.9  | Vol    | tage Unbalance and Converters                     | 47 |

| 2.10 | Vol    | tage Unbalance, Fault Ride-Through and Protection | 51 |

| 2.11 | Vol    | tage Unbalance and DFIG's                         |    |

|      | 2.11.1 | Coordinated Control                               | 54 |

|      | 2.11.2 | Resonant Controllers                              | 55 |

| 2.12 | Cor    | nclusion                                          | 56 |

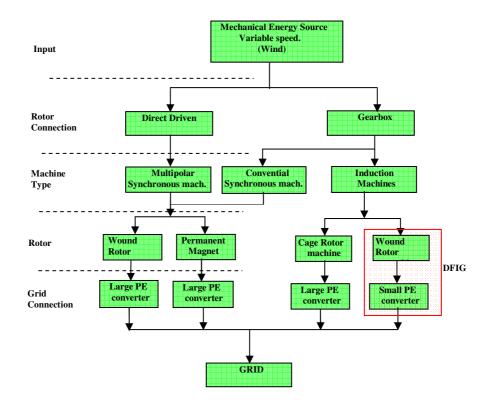

| СН   | APTE   | R 3 WIND POWER TECHNOLOGIES                       | 57 |

| 3.1  | Wir    | nd Power Technologies                             |    |

| 3.2  | Cur    | rrent Wind Turbine topologies                     | 61 |

|      | 3.2.1  | Grid-connected Squirrel Cage Induction Generator  | 61 |

| 3.3  | Wir    | nd Turbine Aerodynamic model                      | 65 |

|      | 3.3.1  | Extraction of power from the air-stream           | 65 |

| 3.4  | Stal   | ll and Pitch Control                              | 66 |

| СН   |        | R 4 INVESTIGATIONS INTO VOLTAGE UNBALANCE         | 68 |

| 4.1  | Inti  | roduction                                                   | 68  |

|------|-------|-------------------------------------------------------------|-----|

| 4.2  | Dis   | tribution Networks - Corneen Wind-Farm                      | 69  |

|      | 4.2.1 | Power Quality Measurement of Wind Farm                      | 70  |

|      | 4.2.2 | Analysis of Voltage Unbalance at Turbine Terminals          | 71  |

|      | 4.2.3 | Analysis of Voltage Unbalance at 10 kV Distribution Voltage | 77  |

| 4.3  | Eff   | ect of Distribution Power Transformers on the Dip Type      |     |

| 4.4  | Ind   | uction Machines and Voltage Unbalance                       | 84  |

|      | 4.4.1 | Simulation                                                  |     |

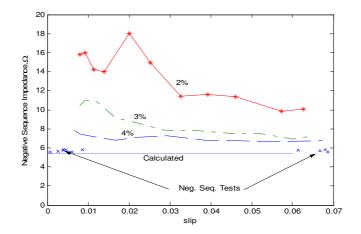

|      | 4.4.2 | Assessment of Negative Sequence Impedance                   | 90  |

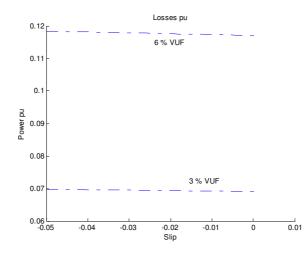

|      | 4.4.3 | Losses in Induction Machine                                 | 92  |

| 4.5  | Unl   | balance Voltage Applied to Converters                       | 93  |

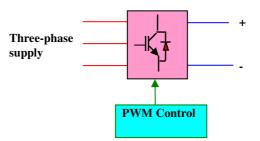

|      | 4.5.1 | Converter - Controlled Rectifier                            | 93  |

|      | 4.5.2 | Inverters                                                   | 96  |

| 4.6  | Dou   | uble-Fed Induction Generators                               |     |

| 4.7  | Syn   | ichronous Generator Systems                                 | 100 |

|      | 4.8.2 | Negative Sequence Calculation                               | 103 |

| 4.9  | Imp   | pact of Voltage Dips                                        | 106 |

| 4.10 | Сог   | nclusion                                                    | 107 |

| СН   |       | R 5 INDUCTION GENERATOR AND DFIG MODELLING                  | 108 |

| 5.1  | Ind   | uction Generator                                            | 108 |

| 5.2  | Ste   | ady State Analysis of Induction Generator                   | 108 |

|      | 5.2.1 | Equivalent Circuit of Induction Machine                     | 109 |

| 5.3  | Dyı   | namic Modelling of the Induction Machine                    | 120 |

|      | 5.3.1 | Space-Vector Notation                                       | 123 |

|                  | 5.3.2    | Three-Phase to Two Phase Representation       |     |

|------------------|----------|-----------------------------------------------|-----|

|                  | 5.3.3    | Induction Machine Dynamic Equations           |     |

| <b>CH</b><br>6.1 |          | R 6 CONTROL OF DFIG                           |     |

|                  |          |                                               |     |

| 6.2              | Rot      | or Side Converter                             |     |

|                  | 6.2.1    | Voltage Equations                             | 141 |

|                  | 6.2.2    | Power and Electromagnetic Torque Equations    |     |

|                  | 6.2.3    | Calculating the Rotor Voltages to be applied  |     |

| 6.3              | Des      | ign of PI Controllers                         | 146 |

|                  | 6.3.1    | Rotor Side Converter                          | 147 |

| 6.3.2            | 2.1 Grie | d Side Converter Control Scheme               |     |

|                  | 6.3.3    | Rotor side and Grid side converter parameters |     |

| 6.4              | Pha      | ise Locked Loop (PLL)                         |     |

| 6.5              | Swi      | tching Patterns                               |     |

|                  | 6.5.1    | Voltage Space Vectors with d-q axis           | 165 |

| 6.6              | Moo      | delling in Simulink/Matlab                    | 168 |

| 6.7              | Res      | ults                                          |     |

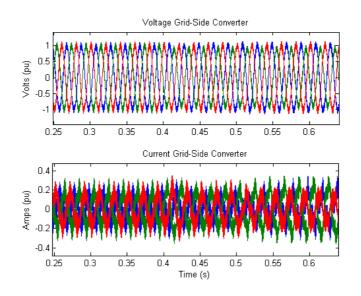

|                  | 6.7.1    | Voltage and Current Distortion                |     |

|                  | 6.7.2    | Third Harmonic Voltage and Current Distortion | 175 |

|                  | 6.6.2    | Conclusions from simulation results           |     |

|                  |          |                                               |     |

# CHAPTER 7 VOLTAGE UNBALANCE COMPENSATION TECHNIQUES..178

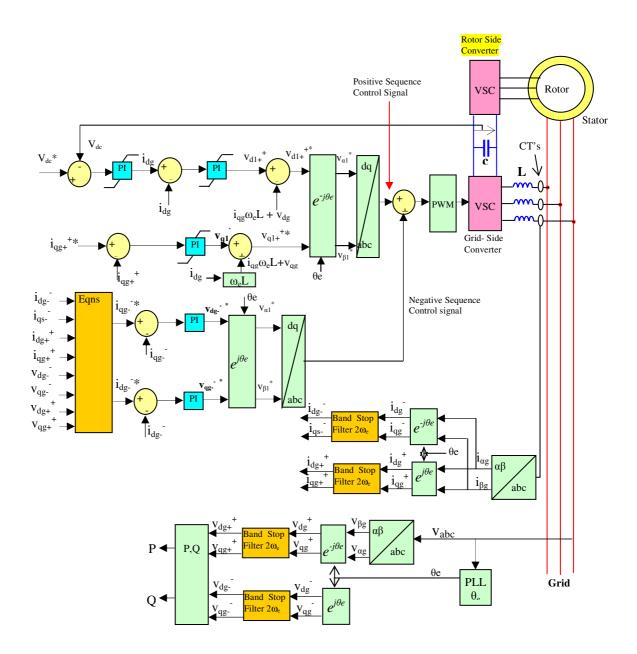

| 7.1 | Control of DFIG Under Network Voltage Unbalance Conditions | 79 |

|-----|------------------------------------------------------------|----|

| 7.2 | Control of Rotor Side Converter – Parallel Control Scheme  | 84 |

|                                                                       | 7.2.1                                             | Stator Power Equations                                                                                                                                                                                          |                |

|-----------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                                                       | 7.2.2                                             | DFIG Torque Equations                                                                                                                                                                                           |                |

| 7.3                                                                   | Gri                                               | d-Side Converter Compensation Techniques                                                                                                                                                                        |                |

| 7.4                                                                   | Coo                                               | ordinated Control of Both Power and Torque Pulsations                                                                                                                                                           |                |

|                                                                       | 7.4.1                                             | Simulations Results – Parallel Control Scheme                                                                                                                                                                   |                |

| 7.5                                                                   | Res                                               | onant Control of Rotor Side Converter                                                                                                                                                                           |                |

| 7.6                                                                   | Res                                               | onant Control of Grid Side Converter                                                                                                                                                                            |                |

|                                                                       | 7.6.1                                             | Resonant Control Scheme – Third Harmonic Compensation                                                                                                                                                           |                |

| 7.7                                                                   | Sin                                               | nulations Results – Resonant Control Scheme                                                                                                                                                                     |                |

| 7.8                                                                   | Res                                               | onant Control of Synchronous Generator System                                                                                                                                                                   |                |

| 7.9                                                                   | Cor                                               | clusion                                                                                                                                                                                                         |                |

|                                                                       |                                                   |                                                                                                                                                                                                                 |                |

| СН                                                                    | APTEI                                             | R 8 LABORATORY TEST RIG                                                                                                                                                                                         | 220            |

| CH<br>8.1                                                             |                                                   | R 8 LABORATORY TEST RIG                                                                                                                                                                                         |                |

|                                                                       | Lab                                               |                                                                                                                                                                                                                 |                |

|                                                                       | Lab<br>8.2.1 I                                    | oratory Test Rig                                                                                                                                                                                                | <b>220</b><br> |

| 8.1                                                                   | Lab<br>8.2.1 H<br>Rot                             | Fixed-point arithmetic and representation of numbers                                                                                                                                                            |                |

| 8.1<br>8.3                                                            | Lab<br>8.2.1 I<br>Rot<br>Grie                     | Fixed-point arithmetic and representation of numbers                                                                                                                                                            |                |

| 8.1<br>8.3<br>8.4                                                     | Lab<br>8.2.1 H<br>Rot<br>Griv<br>Sen              | Fixed-point arithmetic and representation of numbers<br>or Side Converter                                                                                                                                       |                |

| <ul><li>8.1</li><li>8.3</li><li>8.4</li><li>8.5</li></ul>             | Lab<br>8.2.1 I<br>Rot<br>Gri<br>Sen<br>Bas        | boratory Test Rig<br>Fixed-point arithmetic and representation of numbers<br>or Side Converter<br>d Side Converter<br>hikron IGBT Modules                                                                       |                |

| <ul><li>8.1</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Lab<br>8.2.1 I<br>Rot<br>Gri<br>Sen<br>Bas        | Fixed-point arithmetic and representation of numbers<br>or Side Converter<br>d Side Converter<br>hikron IGBT Modules<br>e Values of Voltage and Current                                                         |                |

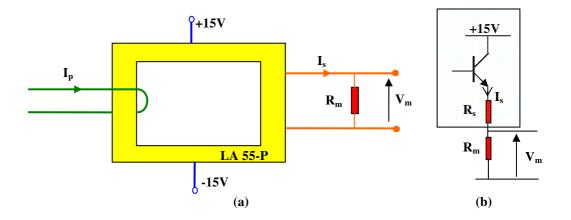

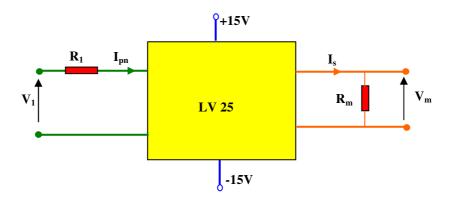

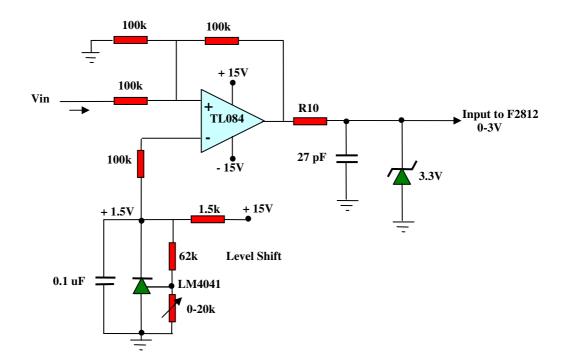

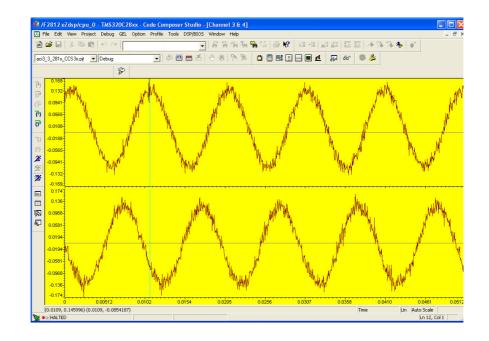

| <ul><li>8.1</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Lab<br>8.2.1 I<br>Rot<br>Gri<br>Sen<br>Bas<br>Cur | Fixed-point arithmetic and representation of numbers<br>or Side Converter<br>d Side Converter<br>hikron IGBT Modules<br>e Values of Voltage and Current<br>rent and Voltage Transducers and Signal Conditioning |                |

| 8.8  | Acq     | uisition of Analogue Variables                   |     |

|------|---------|--------------------------------------------------|-----|

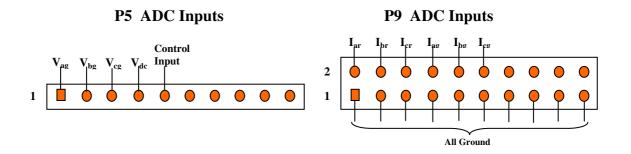

|      | 8.8.1   | Analogue Input Signals to DSP                    |     |

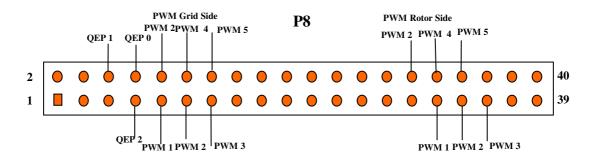

|      | 8.8.1   | Input and Output Connections to DSP              |     |

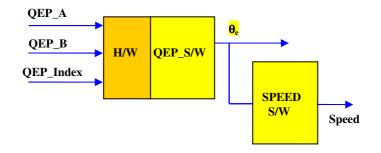

| 8.9  | Spee    | ed and Position Acquisition                      |     |

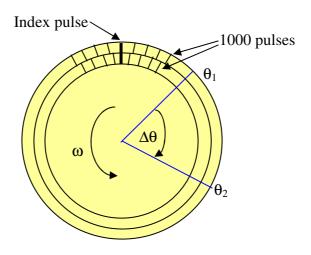

|      | 8.9.1   | Shaft Encoder                                    |     |

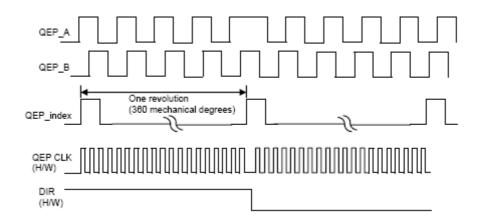

|      | 8.9.1.1 | TI Implementation of QEP                         |     |

|      | 8.9.1.2 | Determination of Reference Frame Angles with PLL |     |

|      | 8.9.1.3 | Determination of Slip Frequency With PLL         |     |

|      | 8.10    | DC-link capacitance                              |     |

|      | 8.11    | Grid-Side line filter                            |     |

| 8.12 | Cod     | e Structure                                      |     |

|      | 8.12.1  | ADC                                              |     |

| СН   | APTE    | R 9 TEST RESULTS                                 | 264 |

| 9.1  | DFI     | G Testing – Stand Alone Operation                |     |

|      | 9.1.2   | Operation With Unbalanced Resistance Load        |     |

|      | 9.1.4   | Grid Side Converter Test                         |     |

| 9.2  | DFI     | G Testing – Grid Connection                      |     |

|      | 9.2.2   | Induction Generator Connected to the Grid        |     |

| 9.3  | DFI     | G Testing –Conclusion                            |     |

|      |         |                                                  |     |

| СН   | APTE    | R 10 CONCLUSION                                  | 279 |

|      |         | R 10 CONCLUSION                                  |     |

| 10.1 | Contrib |                                                  |     |

## **APPENDICES 302**

| Арре | endix A . |                                              | 2  |

|------|-----------|----------------------------------------------|----|

|      | A1        | Plant and Equipment                          | )2 |

|      | A2        | Base Values                                  | )3 |

| Арре | endix B . |                                              | 4  |

| Арре | endix C . |                                              | 5  |

|      | C1        | Current & Voltage Transducers                | )5 |

|      | C1.1      | Current Transducers                          | )5 |

|      | C1.3      | LEM Data Sheets                              | )6 |

| Арре | endix D . |                                              | 8  |

| Арре | endix E . |                                              | 9  |

| Арре | endix F   |                                              | 3  |

|      | F.1       | TI TMS320F2812                               | 13 |

| Арре | endix G . |                                              | 4  |

|      | G1.1      | TMS320F2812 Software and Programming Details | 14 |

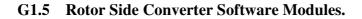

|      | G1.5      | Rotor Side Converter Software Modules        | 17 |

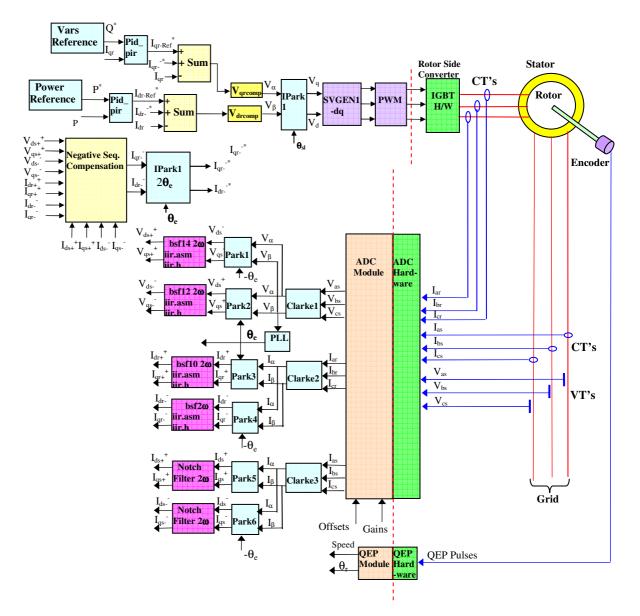

|      | G1.6      | Grid Side Converter Software Modules         | 18 |

| Арре | endix H . |                                              | 1  |

|      | H1        | Semikron Info                                | 21 |

| Арре | endix I   |                                              | 3  |

| Арре | endix J   |                                              | 4  |

| List | of Public | rations                                      | 5  |

| List | of | Figures |

|------|----|---------|

|------|----|---------|

| List of Tables                                                                          | 19  |

|-----------------------------------------------------------------------------------------|-----|

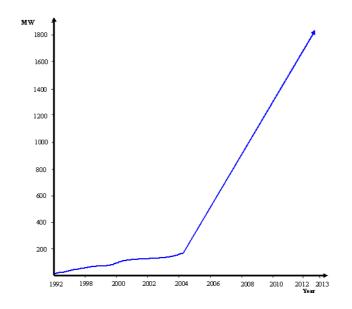

| Figure 1.1 Increase in installed wind energy capacity in Eire                           | 26  |

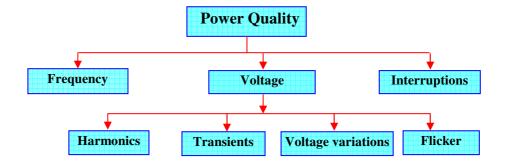

| Figure 2.1 General characteristics of power quality.                                    | 32  |

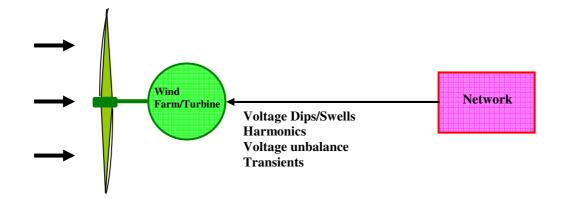

| Figure 2.2 Influence of network power quality on wind farms                             | 33  |

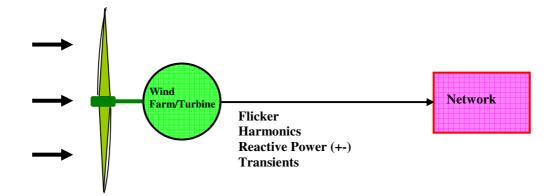

| Figure 2.3 Influence of wind farm power quality on network                              | 33  |

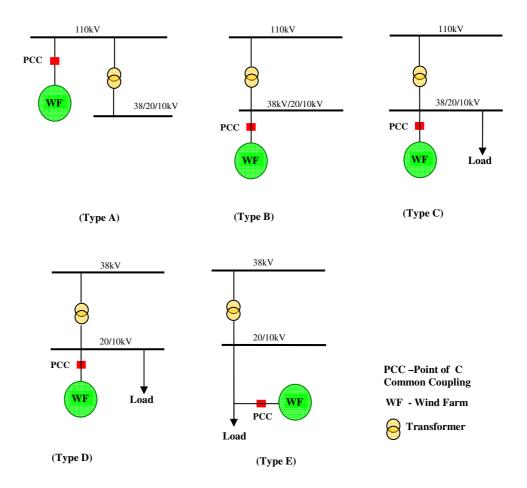

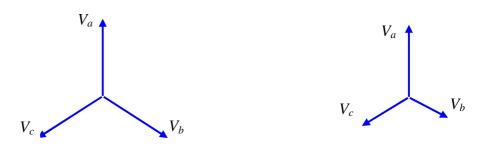

| Figure 2.4 Classification of wind farm power stations connected to Ireland's distributi | ion |

| system                                                                                  | 37  |

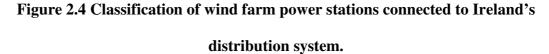

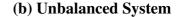

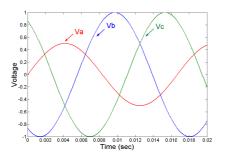

| Figure 2.5 Representation of a balanced and unbalanced three-phase voltage              | 39  |

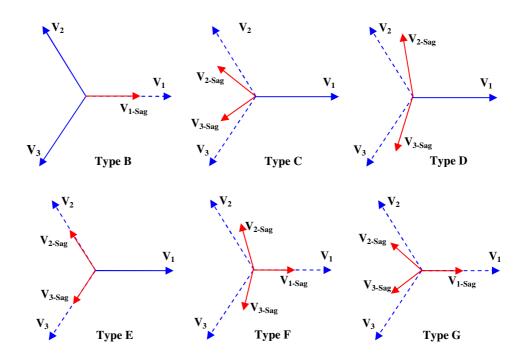

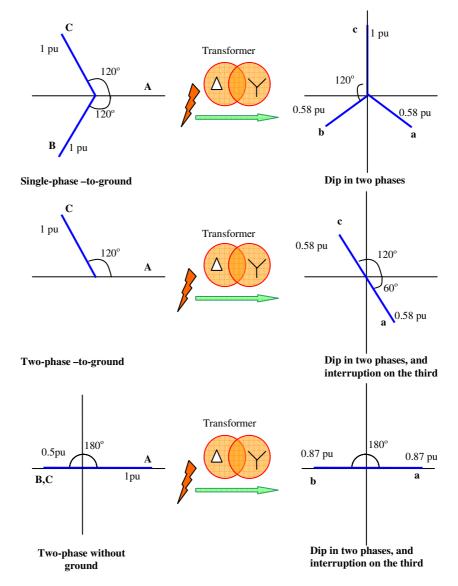

| Figure 2.5 Phasor diagrams of voltage unbalance sags                                    | 44  |

| Figure 2.6 Typical line current waveform of a three-phase diode rectifier               | 48  |

| system when the supply system is balanced                                               | 48  |

| Figure 2.7 Line current waveforms of a three-phase diode rectifier system when the      | 49  |

| supply system is unbalanced                                                             | 49  |

| Figure 3.1 Technologies of wind turbines                                                | 58  |

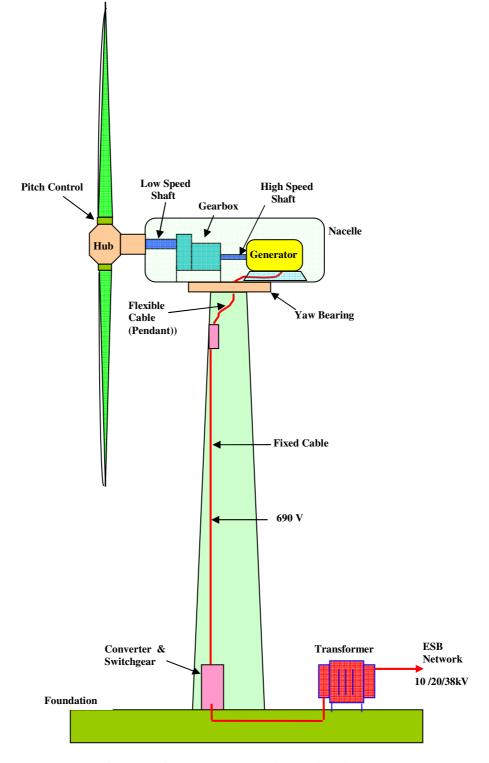

| Figure 3.2 Typical wind turbine components including induction generator, DFIG          |     |

| converter and three-phase transformer (not to scale).                                   | 60  |

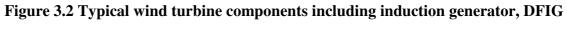

| Figure 3.3 Induction generator fixed-speed wind turbine                                 | 61  |

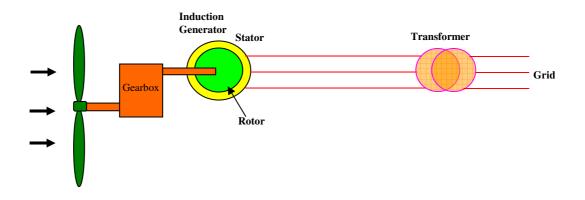

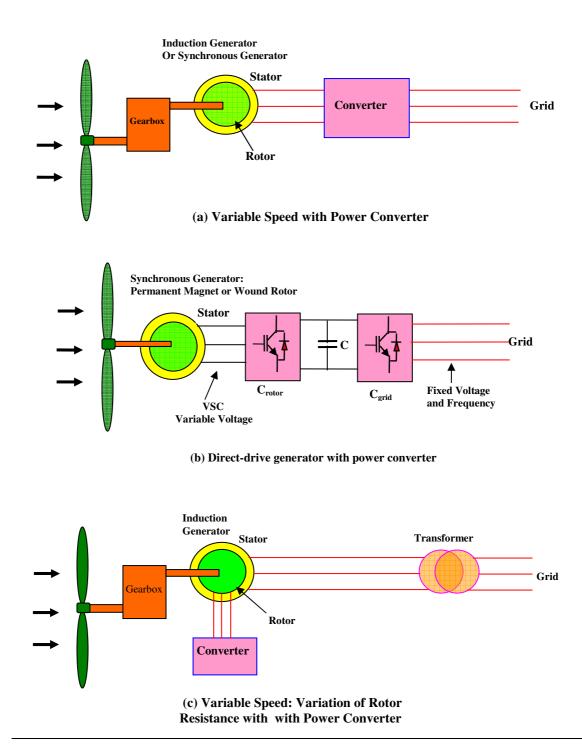

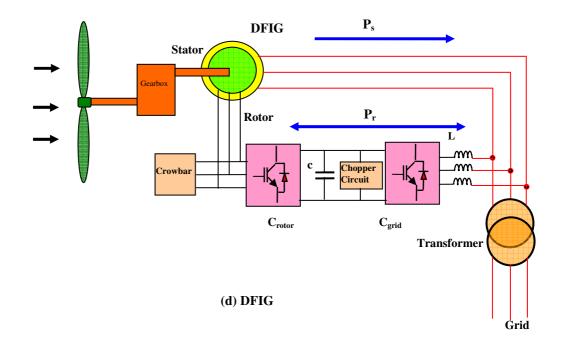

| Figure 3.4 Wind Turbine Systems: Induction Generator and Synchronous Generator, (       | (a) |

| Variable Speed Operation, (b) Direct Drive Variable Speed, (c) Variable Speed:          |     |

| Variation of Rotor Resistance with Power Converter (d) DFIG Variable Speed              | 63  |

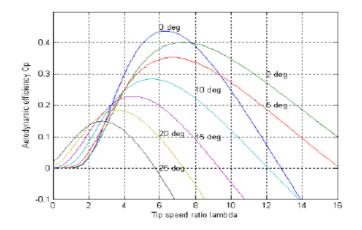

| Figure 3.5 Power coefficient Cp curves as a function of tip speed ratio & pitch angle   | 66  |

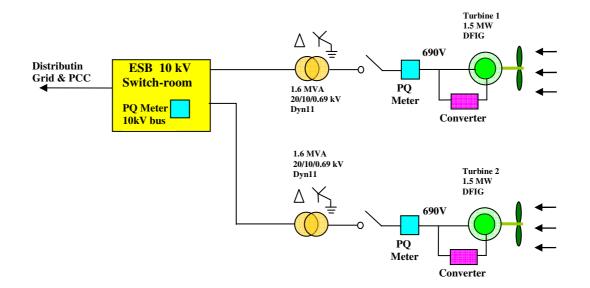

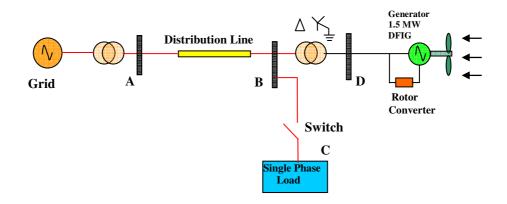

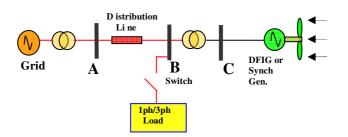

| Figure 4.1 Corneen wind-farm single line diagram                                        | 70  |

| Figure 4.2 Voltage sag at the terminals of a turbine                                    | 71  |

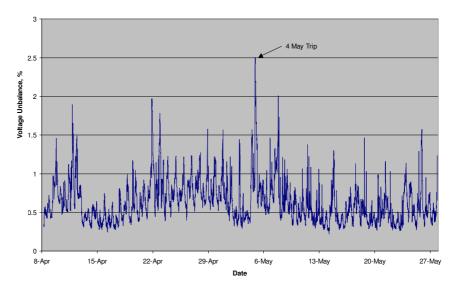

| Figure 4.3 Voltage unbalance (%) recorded on Turbine 2 over seven weeks                 | 72  |

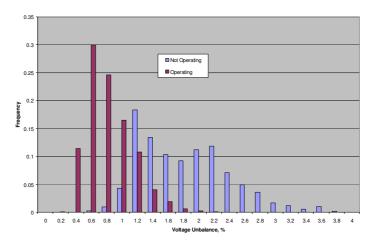

| Figure 4.4 Distribution of voltage unbalance                                       | _ 72 |

|------------------------------------------------------------------------------------|------|

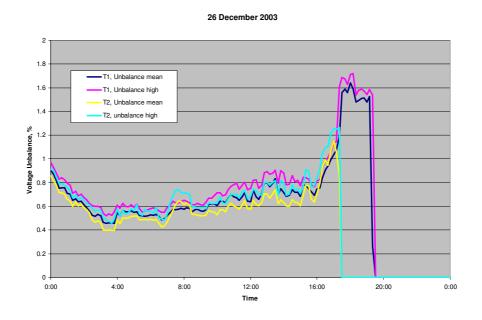

| Figure 4.5 Voltage unbalance (%) at Turbine 1                                      | 74   |

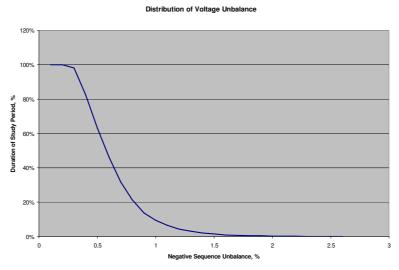

| Figure 4.6 Distribution of voltage unbalance for Turbine 1                         | _ 74 |

| Figure 4.7 Negative sequence voltage on Turbines 1 and 2                           | _ 75 |

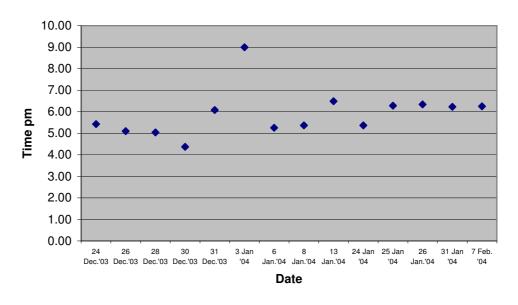

| Figure 4.8 Turbine 2 fault times, Christmas holidays                               | _ 76 |

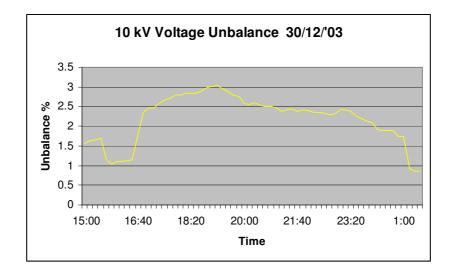

| Figure 4.9 Switch Room 10 kV voltage unbalance                                     | _ 77 |

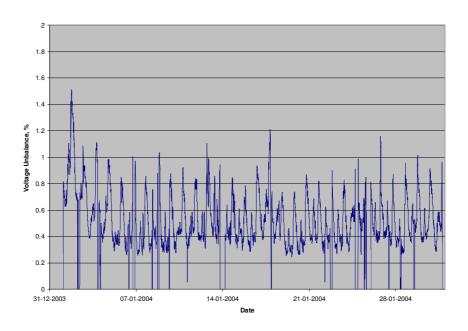

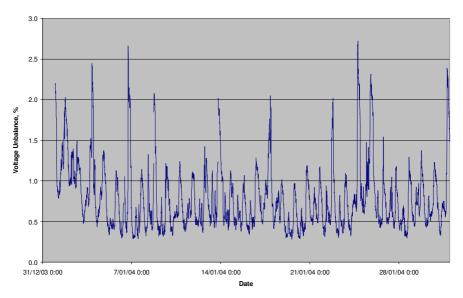

| Figure 4.10 Voltage unbalance (%) at the 10kV bus for January 2004                 | _ 77 |

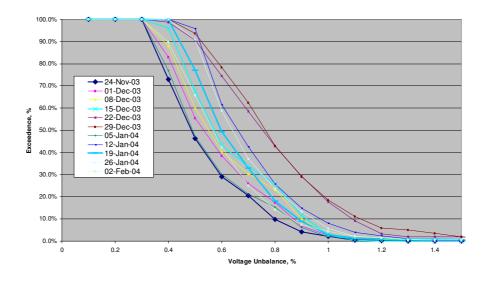

| Figure 4.11 Distribution of voltage unbalance at 10 kV bus during operating and no | on-  |

| operating periods of the turbines                                                  | 78   |

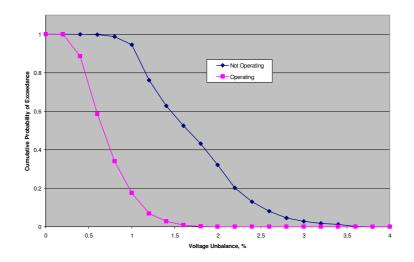

| Figure 4.12 Cumulative probability distribution of voltage unbalance               | _ 79 |

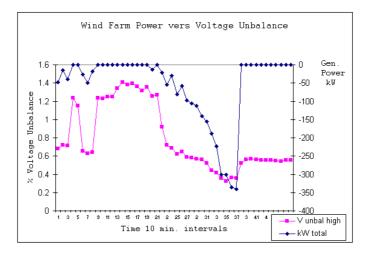

| Figure 4.13 Voltage unbalance and generated power of one turbine at a Wind Farm    | ı in |

| County Cavan. The ION 7600 PQ meter was set for a sampling rate of 10 mins.        | _ 80 |

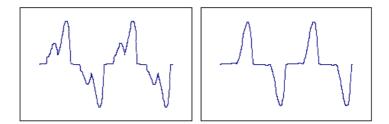

| Figure 4.14 Propagation of voltage dips caused by asymmetrical faults on a Dyl     |      |

| transformer                                                                        | _ 81 |

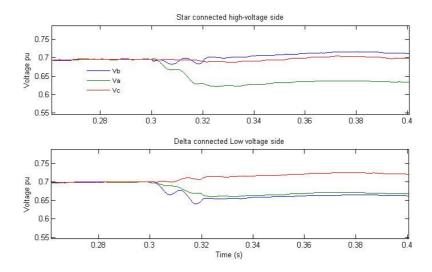

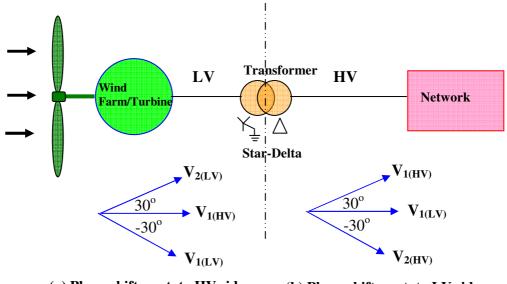

| Figure 4.15 Voltage unbalance propagation through a delta-star transformer         | _ 82 |

| Figure 4.16 Star-delta power transformer located between a wind-turbine and a      |      |

| network; $V_1$ is positive sequence voltage and $V_2$ is negative sequence voltage | _ 83 |

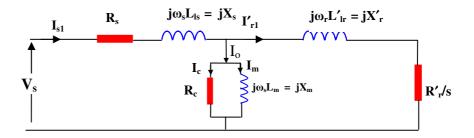

| Figure 4.17 Positive sequence equivalent circuit of an induction machine           | _ 84 |

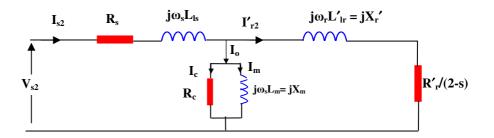

| Figure 4.18 Negative sequence equivalent circuit of an induction machine           | _ 84 |

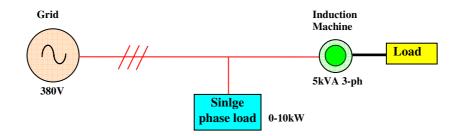

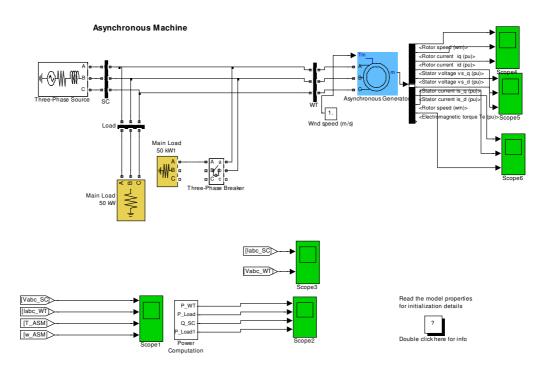

| Figure 4.19 Circuit implemented in Matlab/Simulink                                 | _ 87 |

| Figure 4.20 Simulink model of 5 kW induction machine                               | _ 88 |

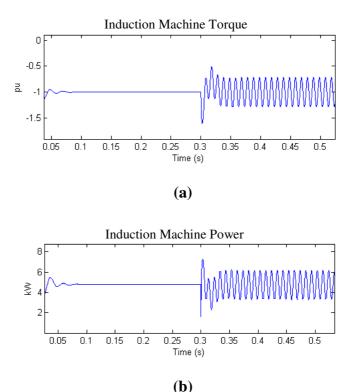

| Figure 4.21 Induction machine: (a) Torque and (b) Stator Power                     | _ 89 |

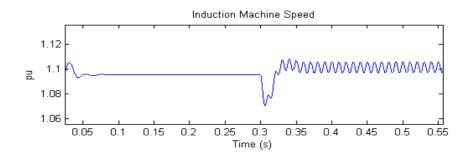

| Figure 4.22 Induction machine speed                                                | _ 89 |

| Figure 4.23 Induction machine circuit for voltage unbalance testing                | _ 90 |

| Figure 4.24 Evaluation of negative sequence model                                  | _ 91 |

| machine                                                                             | _ 93 |

|-------------------------------------------------------------------------------------|------|

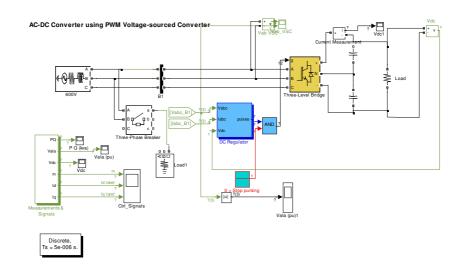

| Figure 4.27 Simulink model of a PWM controlled rectifier                            | _ 95 |

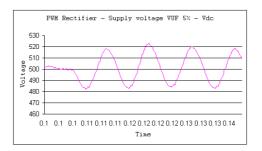

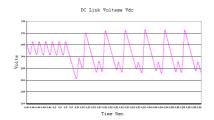

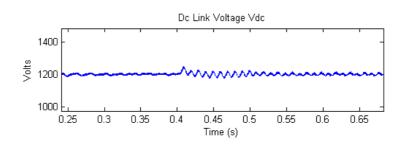

| Figure 4.28 Rectifier DC link voltage V <sub>dc</sub>                               | _ 96 |

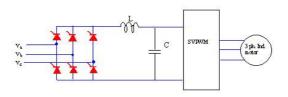

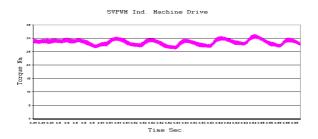

| Figure 4.29 SVPWM Induction Machine Drive                                           | _ 96 |

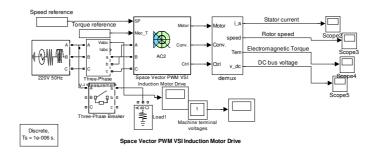

| Figure 4.30 Matlab/Simulink model of space vector PWM VSI induction motor drive     | 97   |

| Figure 4.31 DC Link Voltage of SVPWM Induction Machine Drive                        | _ 97 |

| Figure 4.32 Induction machine torque                                                | _ 98 |

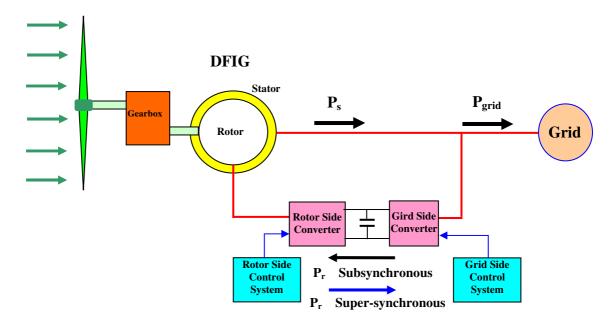

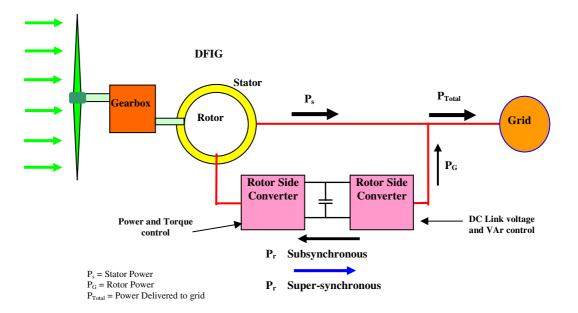

| Figure 4.33 Subsynchronous and super-synchronous power flow in a DFIG               | _ 99 |

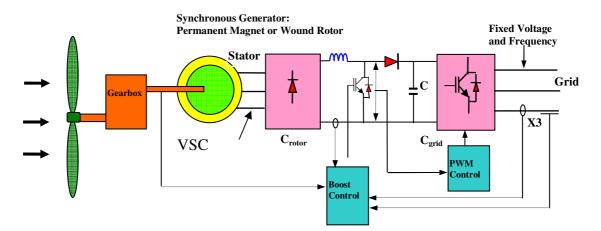

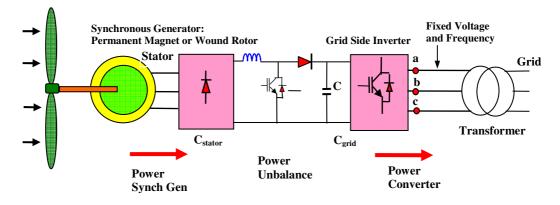

| Figure 4.34 Synchronous Generator System                                            | 101  |

| Figure 4.35 Unbalanced voltage system                                               | 103  |

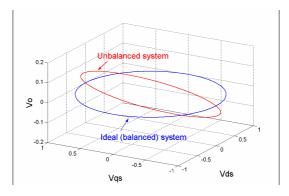

| Figure 4.36 Space vector trajectory of an unbalanced system in the d-q-o plane      | 104  |

| Figure 4.37 Results of a Matlab/Simulink simulation of a DFIG showing the direct an | nd   |

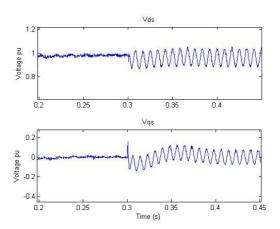

| quadrature components $V_{ds}$ and $V_{qs}$ respectively.                           | 104  |

| Figure 4.38 Results of a Matlab/Simulink simulation of a DFIG showing the direct an | nd   |

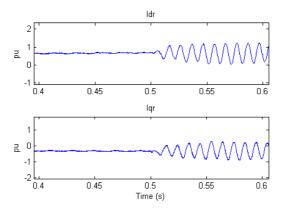

| quadrature components $I_{dr}$ and $I_{qr}$ respectively.                           | 105  |

| Figure 4.39 Sequence Components in the Frequency Domain                             | 105  |

| Figure 4.40 Balanced (a) and unbalanced (b) voltage dips.                           | 106  |

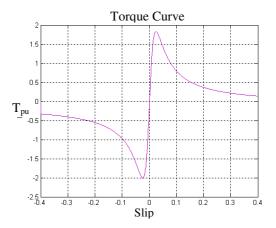

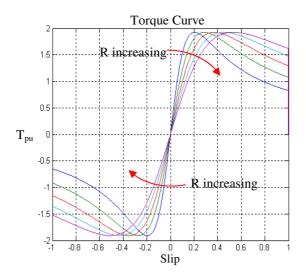

| Figure 5.1 Shaft Torque of the induction machine with a short-circuited rotor, as a |      |

| function rotor speed                                                                | 110  |

| Figure 5.2 Shaft Torque of the induction machine.                                   | 111  |

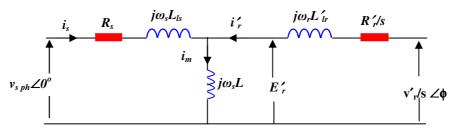

| Figure 5.3 DFIG steady state equivalent circuit                                     | 112  |

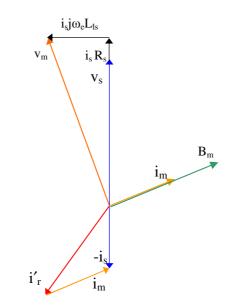

| Figure 5.4 Phasor diagram of simplified equivalent circuit                          | 113  |

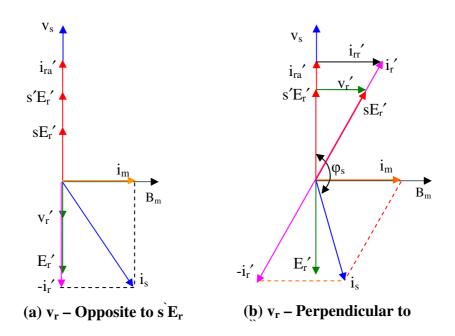

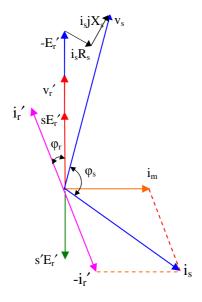

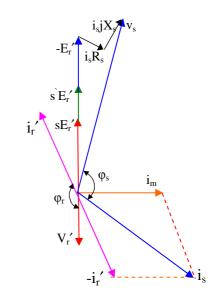

| Figure 5.5 Phasor diagram of DFIG                                                   | 114  |

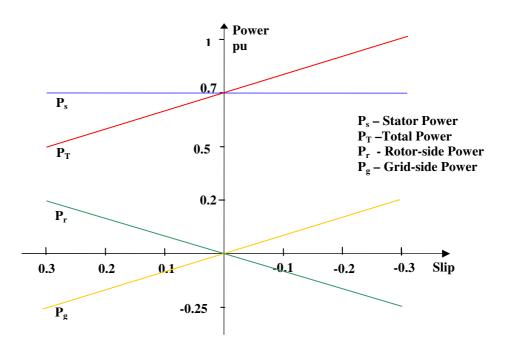

| Figure 5.6 Subsynchronous and super-synchronous power flow in a DFIG.               | 115  |

Figure 4.25 Losses as a result of applied voltage unbalance to an 800 kW induction

| Figure 5.7 Phasor diagram of DFIG                                                                | _ 116            |

|--------------------------------------------------------------------------------------------------|------------------|

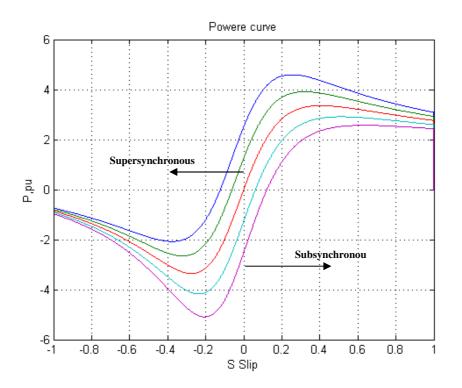

| Figure 5.8 Plots of DFIG power versus slip s.                                                    | _ 117            |

| Figure 5.9 Power flow versus slip in a DFIG                                                      | _ 118            |

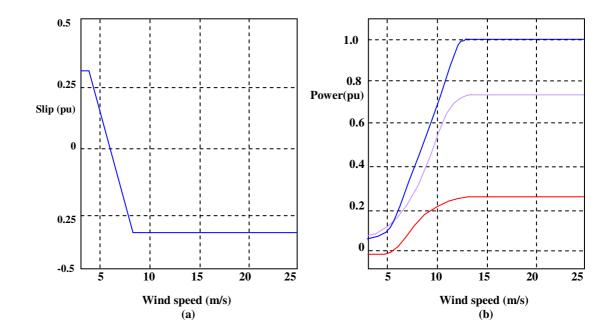

| Figure 5.10 Typical characteristic for a DFIG. (a) Slip as a function of wind speed.             | (b)              |

| Mechanical power (Blue), rotor power (Red) and stator power (purple) as a functio                | n of             |

| wind speed                                                                                       | _ 119            |

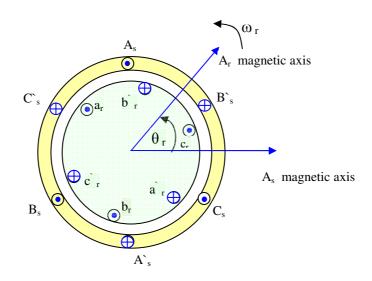

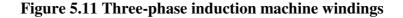

| Figure 5.11 Three-phase induction machine windings                                               | _ 120            |

| Figure 5.12 Three-phase induction machine windings showing space vectors $v_s$ , $i_s$ a         | nd               |

| Ψs                                                                                               | _ 124            |

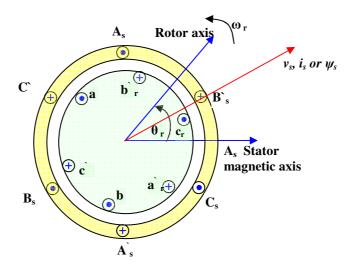

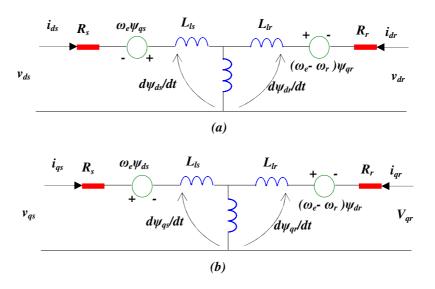

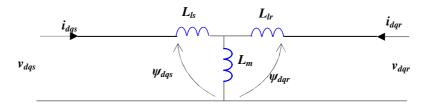

| Figure 5.13 Equivalent circuit of a DFIG in an arbitrary reference frame                         | _ 124            |

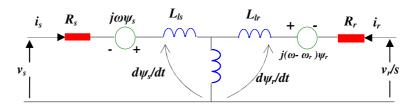

| Figure 5.14 Equivalent two phase machine from three-phase machine using Clark                    |                  |

| Transformation                                                                                   | _ 127            |

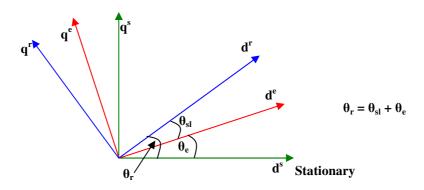

| Figure 5.15 Reference frames where the superscript $(^{s})$ indicates the stationary frame       | ıe,              |

| superscript $(^{e})$ indicates the synchronous frame and superscript $(^{r})$ is the rotor frame | 2.               |

| The position of the rotor reference indicates it is in the supersynchronous region               | _ 129            |

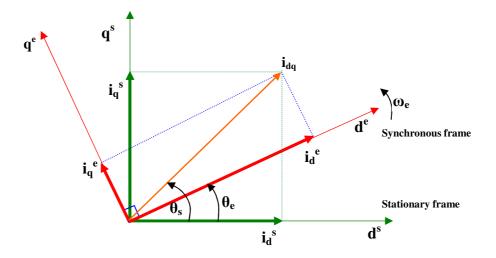

| Figure 5.16 Stationary and synchronous frames.                                                   | _ 130            |

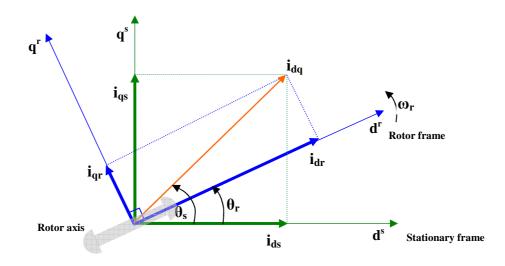

| Figure 5.17 Stationary and rotor reference frames.                                               | _ 131            |

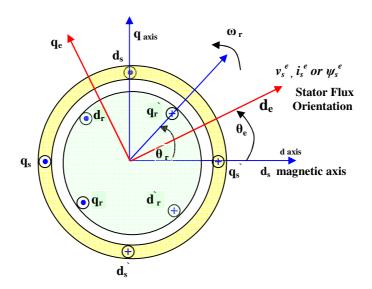

| Figure 5.18 Three-phase induction machine windings, showing space vectors $v_s^e$ , $i_s$        | <sup>e</sup> and |

| $\psi_s^e$ aligned with the synchronous frame                                                    | _ 132            |

| Figure 5.19 dq equivalent circuit in the synchronous reference frame.                            | _ 134            |

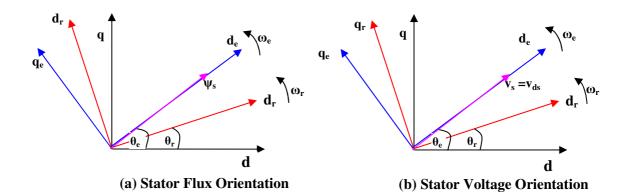

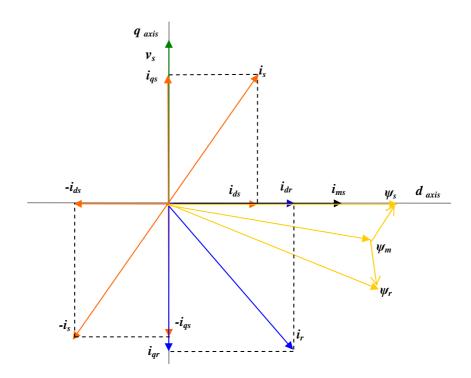

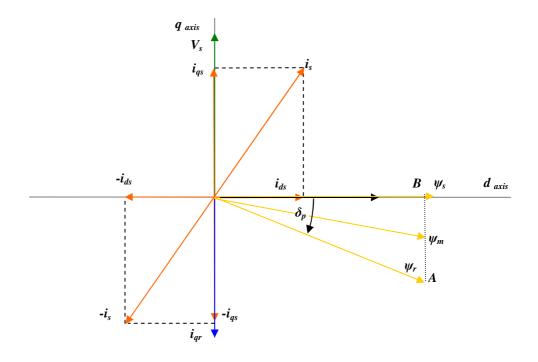

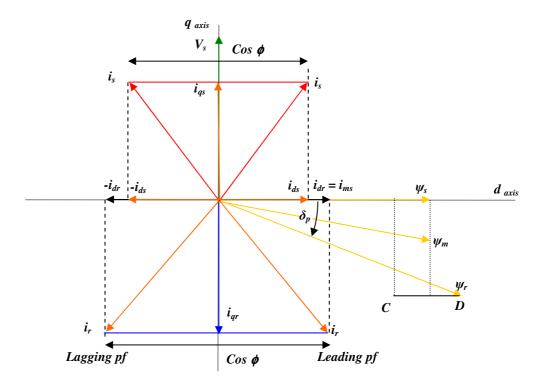

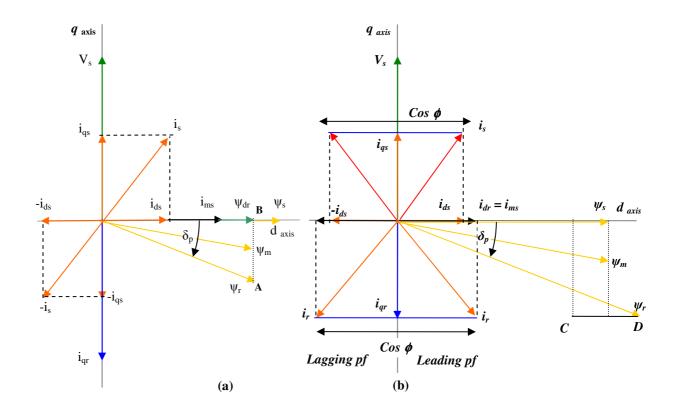

| Figure 5.20 Stator vector orientation                                                            | _ 135            |

| Figure 5.21 Equivalent Circuit in the Stationary Reference Frame                                 | _ 135            |

| Figure 5.22 D-Q Phasor diagram of induction machine with Stator Flux Orientation                 | n                |

| (SFO)                                                                                            | _ 136            |

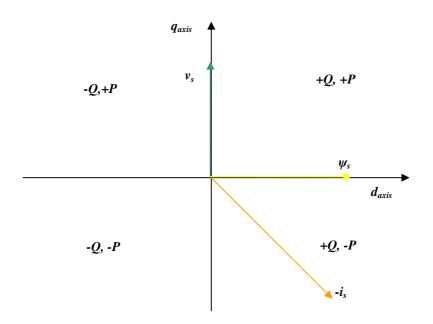

| Figure 5.23 Phasor Diagram Active Power Control.                                                 | _ 136            |

| Figure 5.24 Phasor diagram, constant active power                                 | _ 137 |

|-----------------------------------------------------------------------------------|-------|

| Figure 5.25 Relationship between DFIG power and stator current space vector       | _ 138 |

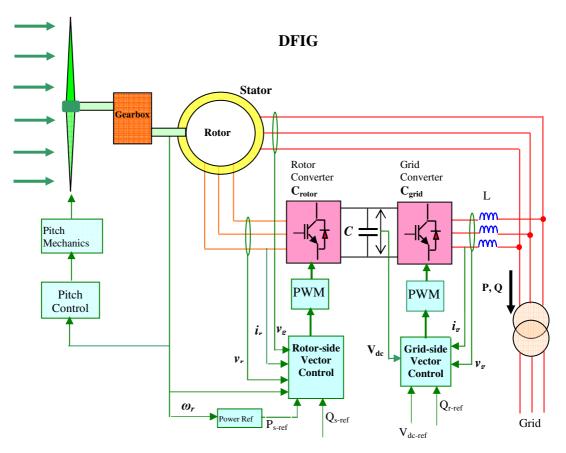

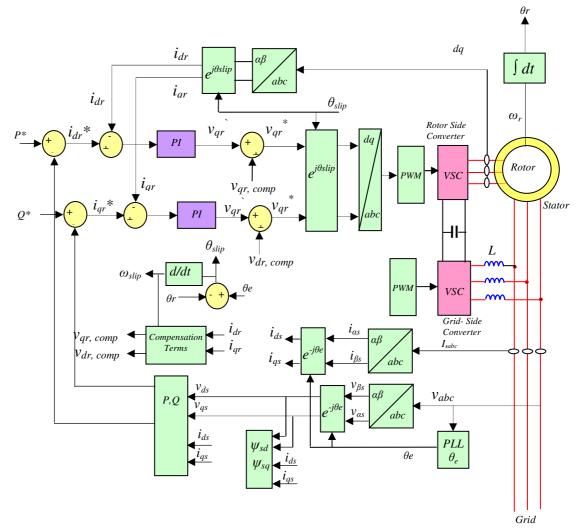

| Figure 6.1 Block diagram of DFIG and control elements                             | _ 140 |

| Figure 6.2 Vector control of rotor-side converter of DFIG                         | _ 146 |

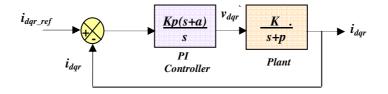

| Figure 6.3 Rotor converter current-control loop                                   | _ 147 |

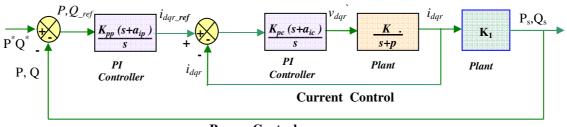

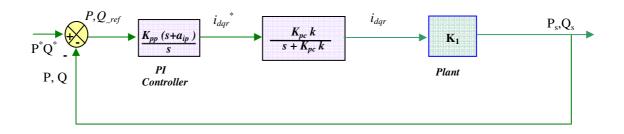

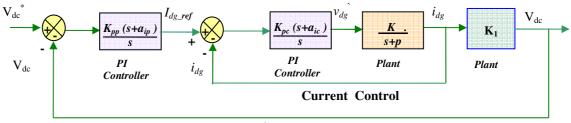

| Figure 6.4 Cascade control structure                                              | _ 149 |

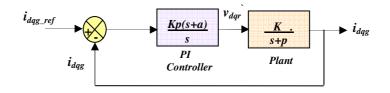

| Figure 6.5 Cascade control structure                                              | _ 150 |

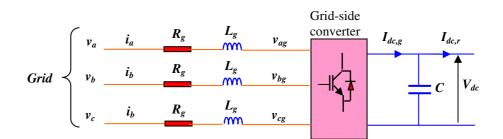

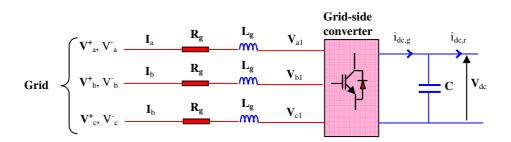

| Figure 6.6 Grid-side converter schematic                                          | _ 152 |

| Figure 6.7 Grid-side converter d-q vector control scheme in grid (stator) voltage |       |

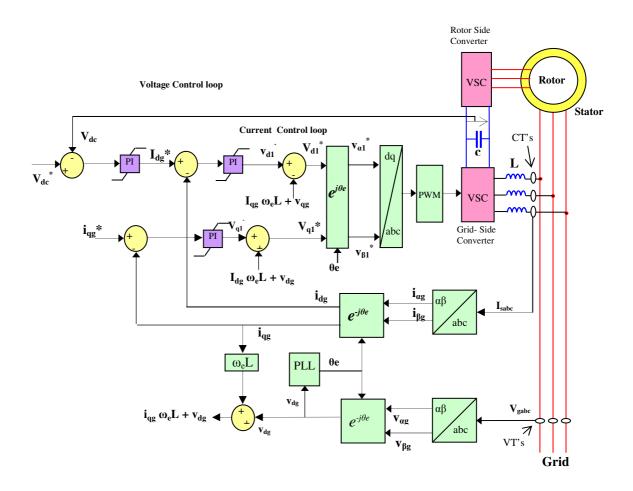

| orientation                                                                       | _ 154 |

| Figure 6.8 Grid-side converter current and voltage control loops                  | _ 157 |

| Figure 6.9 Grid Side converter current-control loop                               | _ 157 |

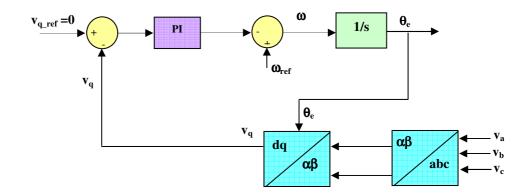

| Figure 6.10 Phase Locked Loop, PLL to obtain $\theta_e$                           | _ 159 |

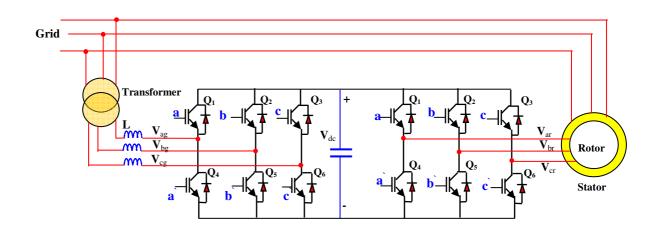

| Figure 6.11 IGBT transistors on rotor side and grid side converters               | _ 160 |

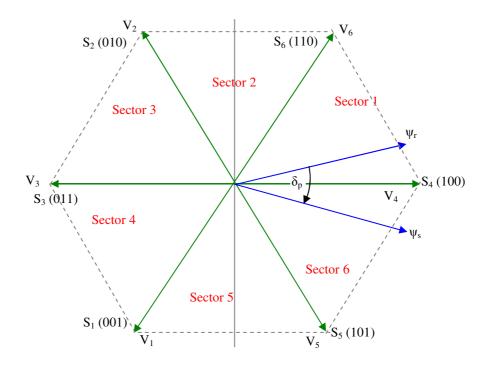

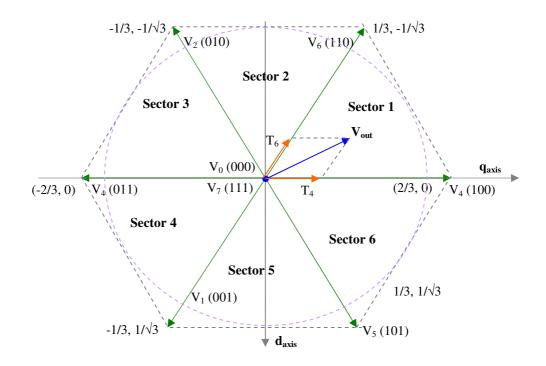

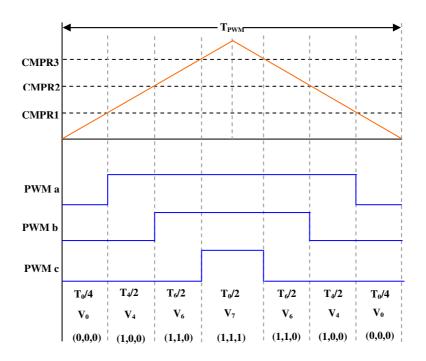

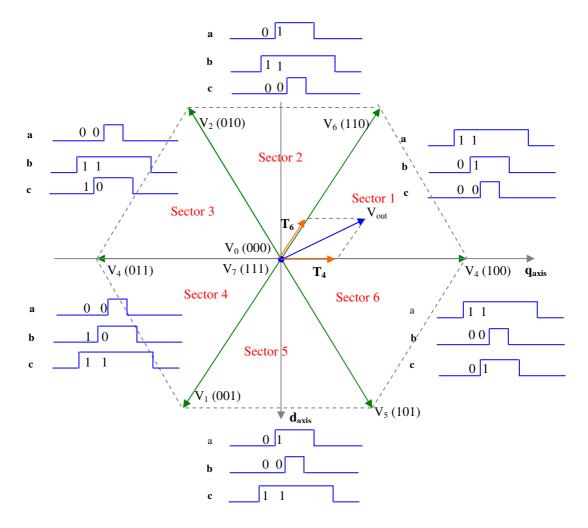

| Figure 6.12 Voltage space vectors                                                 | _ 163 |

| Figure 6.13 Phasor diagram active and reactive power control                      | _ 164 |

| Figure 6.14 Voltage dq space vectors                                              | _ 166 |

| Figure 6.15 Symmetric space vector PWM waveform                                   | _ 167 |

| Figure 6.16 Voltage dq space vectors                                              | _ 168 |

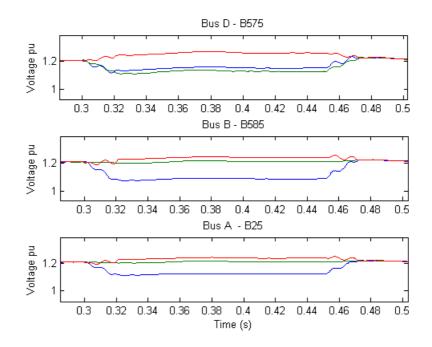

| Figure 6.18 Voltage profile of network busses                                     | _ 171 |

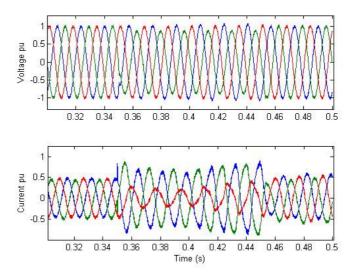

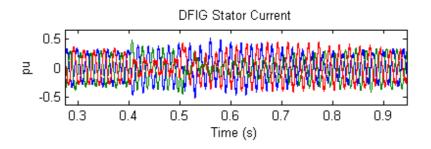

| Figure 6.19 DFIG Stator Voltage and Current                                       | _ 171 |

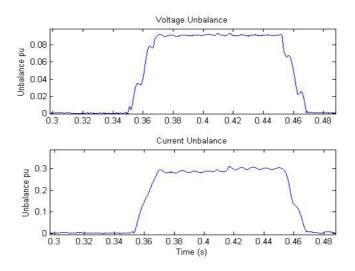

| Figure 6.20 Percentage voltage and current unbalance at DFIG terminals            | _ 172 |

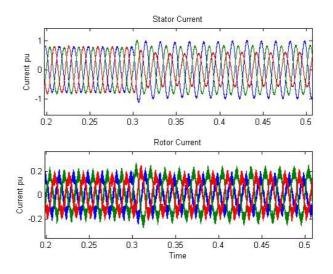

| Figure 6.21 DFIG stator and rotor currents                                        | _ 173 |

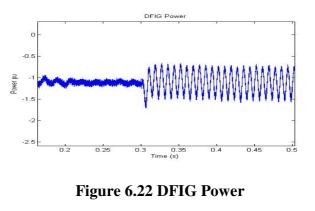

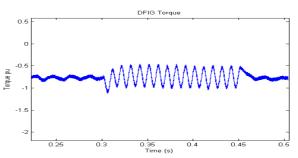

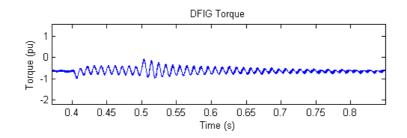

| Figure 6.23 DFIG Torque                                                           | _ 173 |

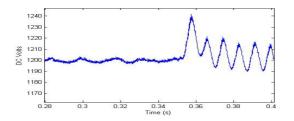

| Figure 6.24 DFIG DC link voltage, V <sub>dc</sub>                                 | _ 174 |

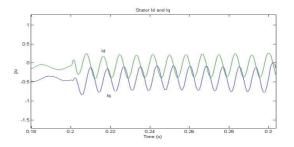

| Figure 6.25 Stator $i_d$ and $i_q$ currents                                              | _ 174 |

|------------------------------------------------------------------------------------------|-------|

| Figure 6.26 Voltage unbalance factor                                                     | _ 175 |

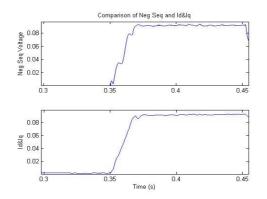

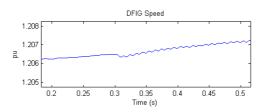

| Figure 6.27 DFIG Speed                                                                   | _ 175 |

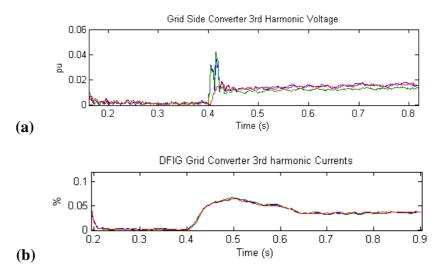

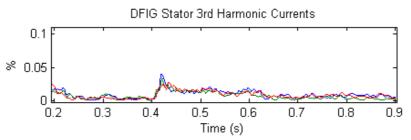

| Figure 6.28 Grid-side converter ac side input third harmonic voltages (a) and third      | !     |

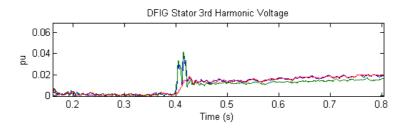

| harmonic currents (b) – Subsynchronous mode of operation                                 | _ 175 |

| Figure 6.29 DFIG stator third harmonic voltages and currents                             | 176   |

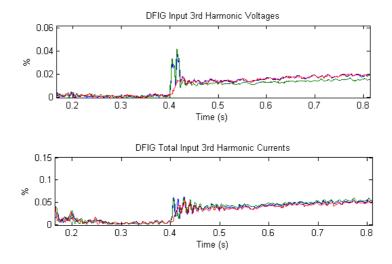

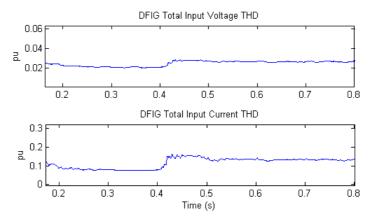

| Figure 6.30 DFIG Total Input 3 <sup>rd</sup> harmonic voltages and currents – full power | _ 176 |

| <i>Figure 6.31 DFIG terminal voltage THD and current THD – full power</i>                | _ 177 |

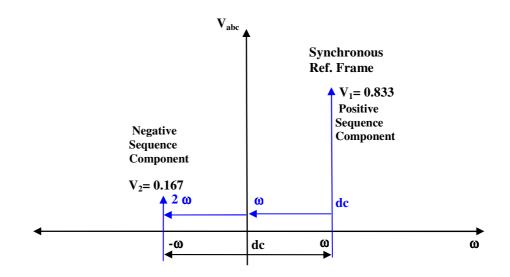

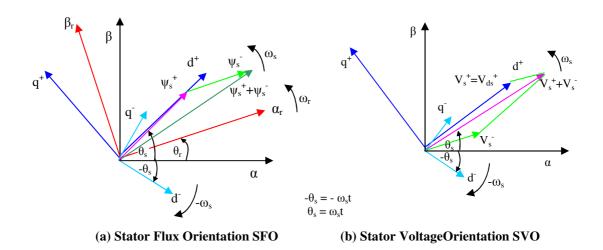

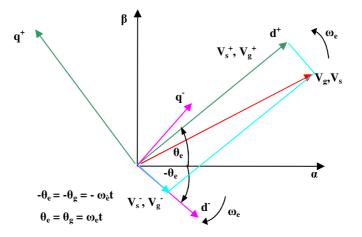

| Figure 7.1 Reference frame orientation.                                                  | _ 180 |

| Figure 7.2 Positive sequence reference frame equivalent circuit                          | _ 181 |

| Figure 7.3 Negative sequence reference frame equivalent circuit                          | _ 181 |

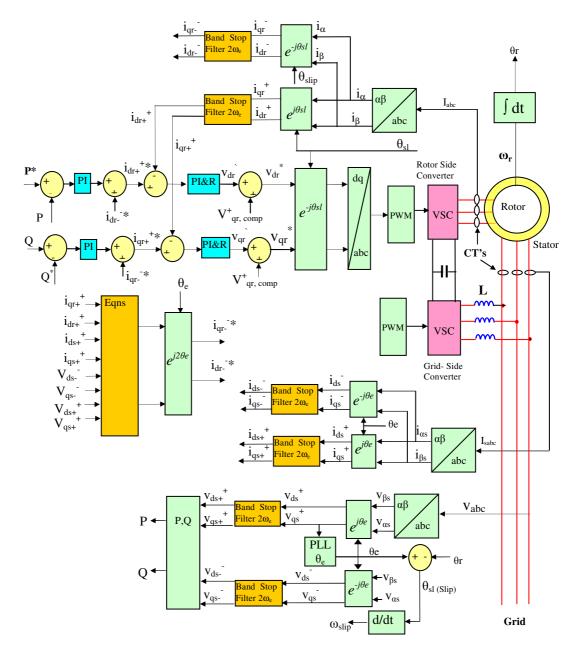

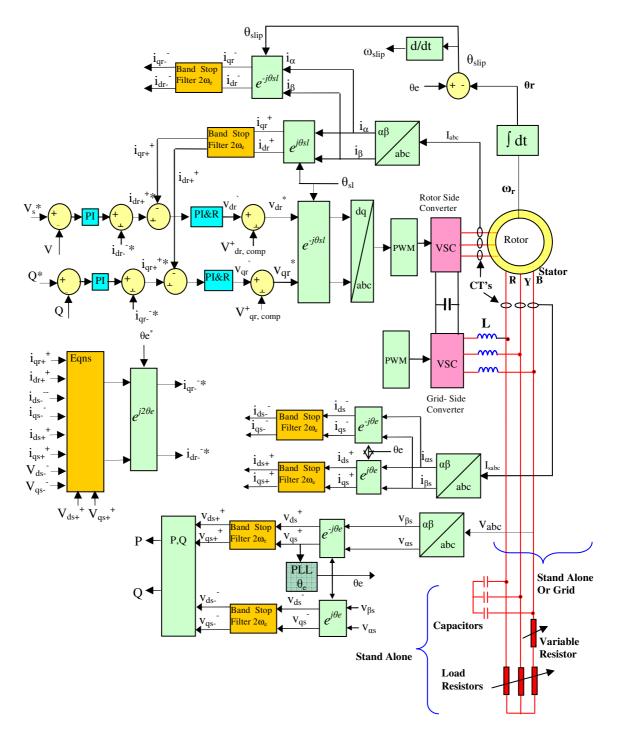

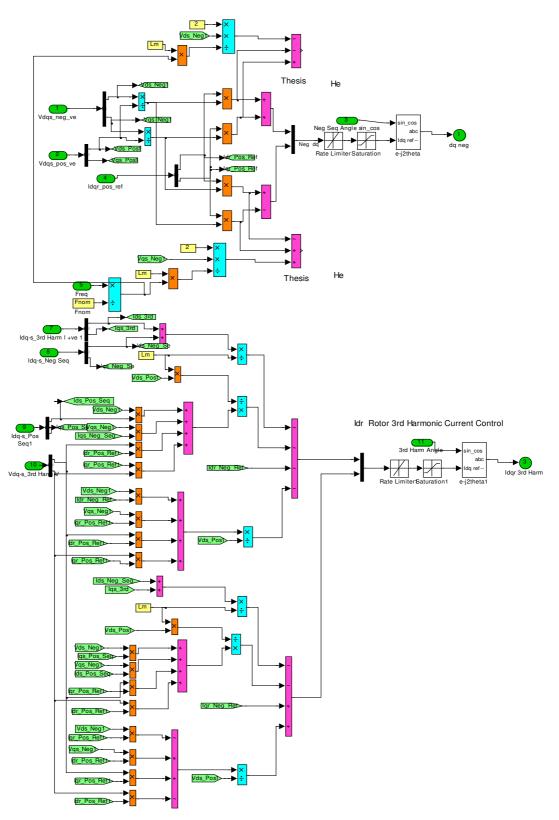

| Figure 7.4 DFIG rotor side converter control including compensation scheme               | _ 192 |

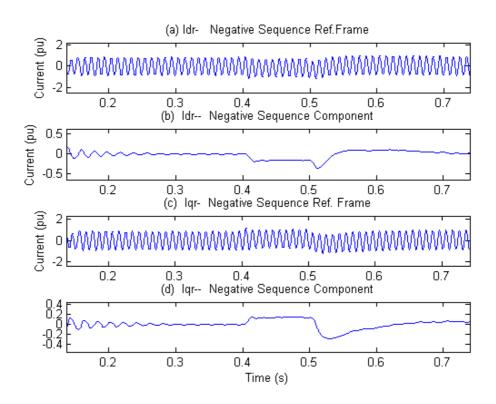

| Figure 7.5 Negative sequence reference frames and components                             | _ 193 |

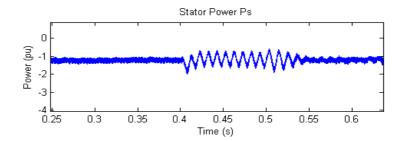

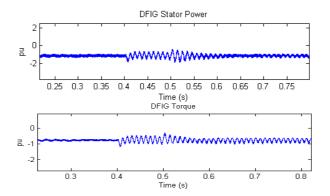

| Figure 7.6 DFIG stator power                                                             | _ 195 |

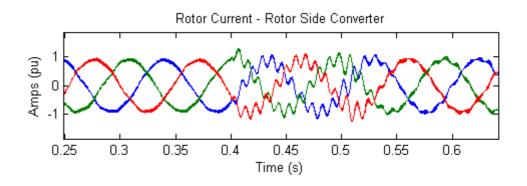

| Figure 7.7 DFIG rotor side converter rotor currents                                      | _ 195 |

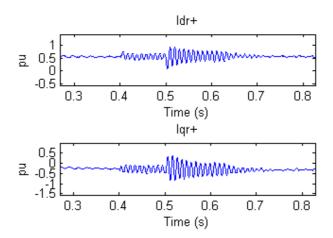

| Figure 7.8 DFIG positive sequence rotor side control currents $I_{dr}$ and $I_{qr}$      | _ 196 |

| Figure 7.9 DFIG torque                                                                   | _ 196 |

| Figure 7.10 Grid-side converter schematic when network supply is unbalanced              | _ 197 |

| Figure 7.11 Grid side converter control scheme including parallel negative sequent       | ce    |

| compensation                                                                             | _ 201 |

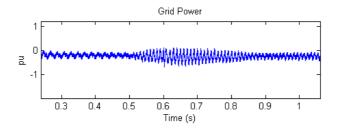

| Figure 7.12 Grid side voltage and current plots                                          | _ 202 |

| Figure 7.13 DC link voltage V <sub>dc</sub>                                              | _ 202 |

| Figure 7.14 Grid-side real power                                                         | _ 203 |

| Figure 7.14 D-Q reference frame orientation.                                             | _ 204 |

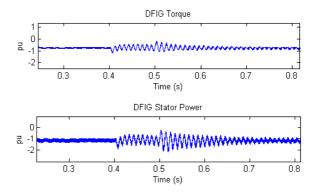

| Figure 7.15 DFIG stator power and torque – stator power compensation                     | _ 206 |

| Figure 7.16 DFIG stator power and torque – Torque Compensation                         | 207     |

|----------------------------------------------------------------------------------------|---------|

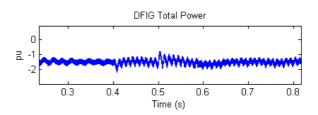

| Figure 7.17 DFIG total power – no grid side compensation                               | 207     |

| Figure 7.18 DFIG total power – grid side compensation                                  | 207     |

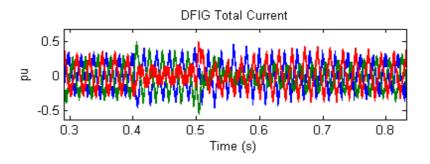

| Figure 7.19 DFIG total current                                                         | 208     |

| Figure 7.20 Stator Current                                                             | 208     |

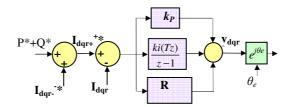

| Figure 7.21 Rotor Side PI and Resonant Controller                                      | 209     |

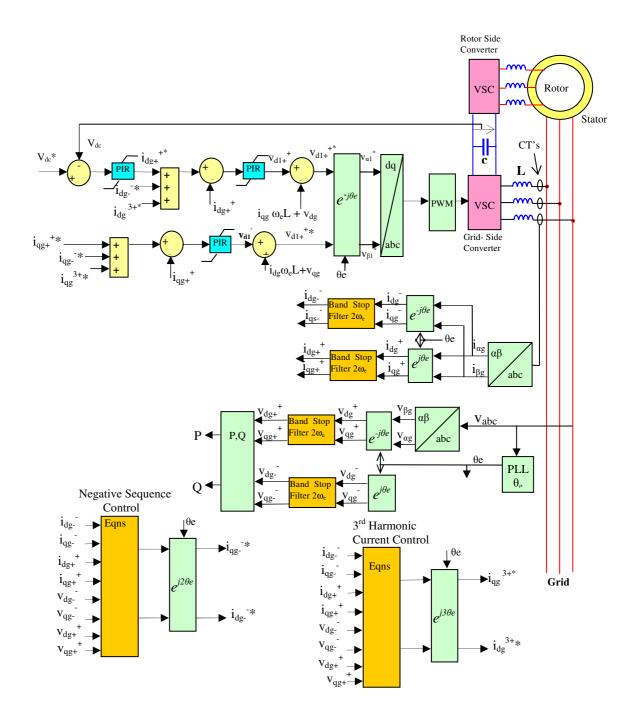

| Figure 7.22 DFIG rotor side converter control including compensation scheme            | 210     |

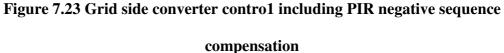

| Figure 7.23 Grid side converter control including PIR negative sequence comper         | isation |

|                                                                                        | 212     |

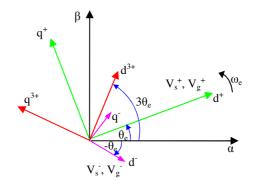

| <i>Figure 7.24 DQ positive, negative and 3<sup>rd</sup> harmonic reference frames.</i> | 213     |

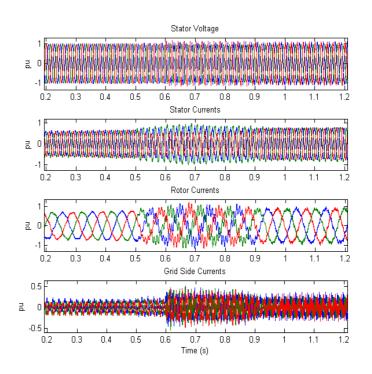

| Figure 7.25 Results for PIR Control Scheme                                             | 213     |

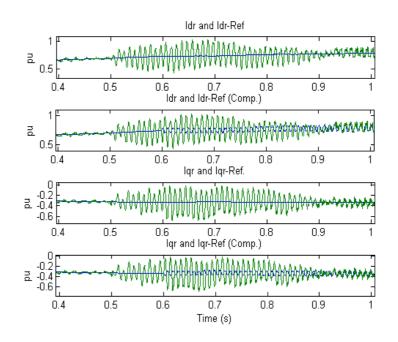

| Figure 7.26 Rotor Side Converter Idr and Iqr currents                                  | 214     |

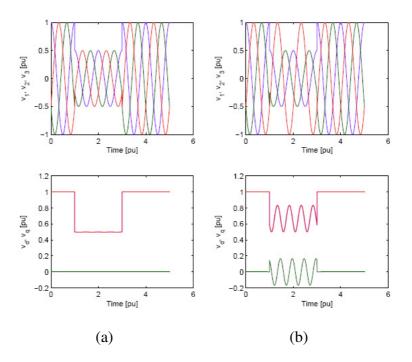

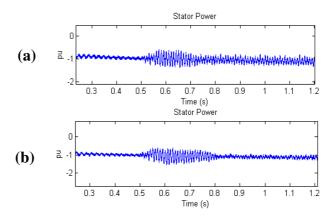

| Figure 7.27 Stator Power ((a)-Standard Control- (b) PIR Compensation)                  | 215     |

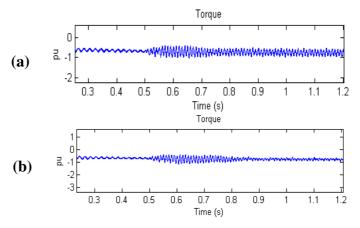

| Figure 7.28 DFIG Torque (a) no compensation (b) compensation                           | 215     |

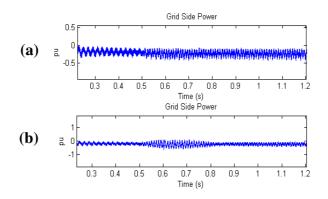

| Figure 7.29 Grid Side Power (a) no compensation (b) compensation                       | 216     |

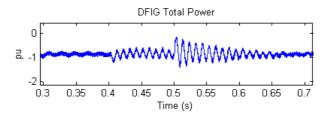

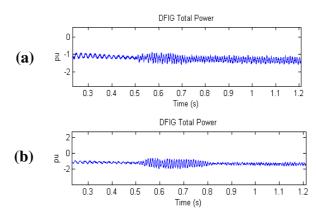

| Figure 7.30 DFIG Total Power (a) no compensation (b) compensation                      | 216     |

| Figure 7.31 Synchronous Generator Network Model                                        | 217     |

| Figure 7.32 Synchronous Generator System                                               | 218     |

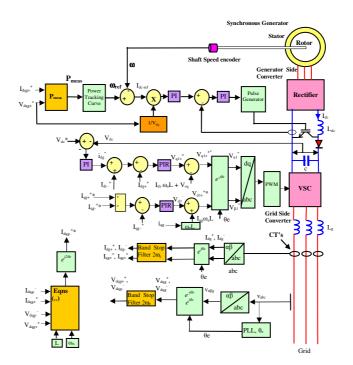

| Figure 7.33 Synchronous Generator Control Scheme                                       | 218     |

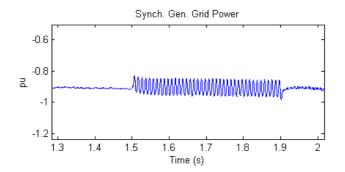

| Figure 7.34 Synchronous Generator System Grid Power                                    | 219     |

| Figure 8.1 Double-Fed Induction Machine                                                | 221     |

| Figure 8.2 eZdsp <sup>TM</sup> TMS320F2812 PCB connector positions                     | 223     |

| Figure 8.3 eZdsp <sup>TM</sup> TMS320F2812 and interface connector board               | 224     |

| Figure 8.4 Rotor side converter                                                        | 226     |

| Figure 8.5 Grid side converter                                                         | 227     |

| Figure 8.6 IGBT over current protection                                                                                                                          | 229        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 8.7 Connection of current transducer LA 55-P                                                                                                              | 233        |

| Figure 8.8 Connection of the voltage transducer LV 25-P.                                                                                                         | 235        |

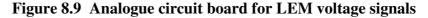

| Figure 8.9 Analogue circuit board for LEM voltage signals                                                                                                        | 239        |

| Figure 8.10 Analogue circuit board for LEM current signals                                                                                                       | 241        |

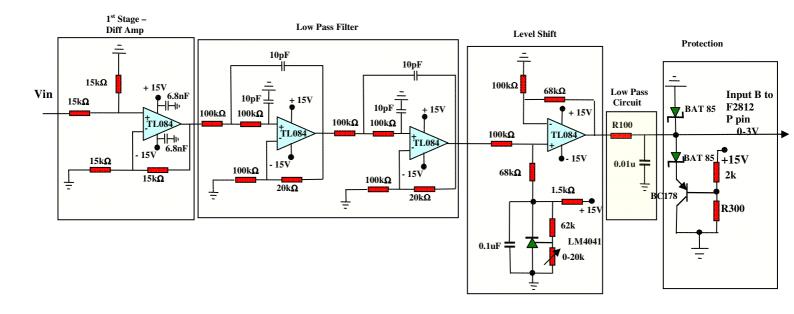

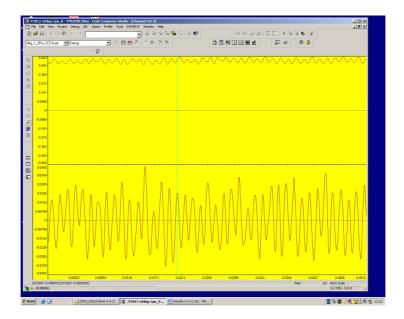

| Figure 8.11 Code Composer Studio – measurement of TI F2812 current at 1.5A                                                                                       | 242        |

| Figure 8.12 Compensating circuit                                                                                                                                 | 243        |

| Figure 8.13 Measurement of F2812 current signal at 1.5A with insertion of                                                                                        |            |

| compensating circuit                                                                                                                                             | 243        |

| Figure 8.14 Code Composer Studio – Measurement of DSP current signal at 4.5A w                                                                                   | ith        |

| insertion of compensating circuit                                                                                                                                | 244        |

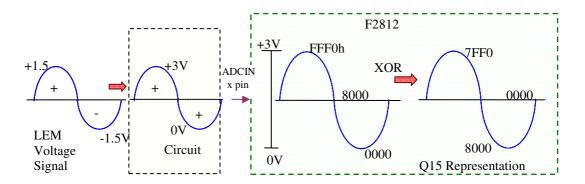

| Figure 8.15 DSP analogue input and number conversion scheme for bipolar input                                                                                    |            |

| signals                                                                                                                                                          | 244        |

| Figure 8.16 DSP interface input connectors                                                                                                                       | 247        |

| Figure 8.17 Incremental shaft encoder                                                                                                                            | 248        |

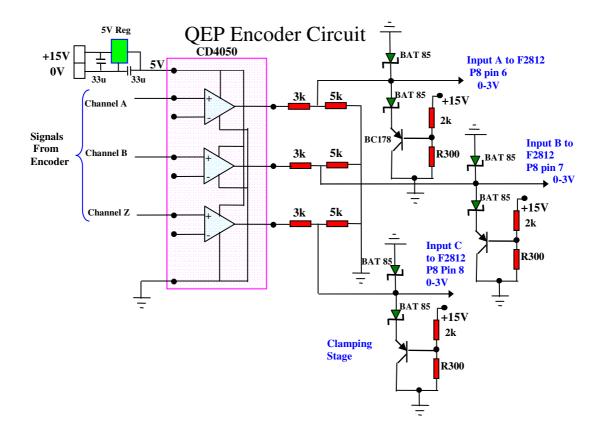

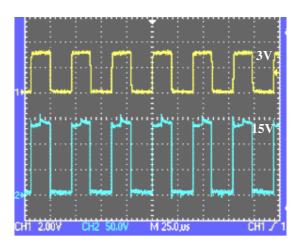

| Figure 8.18 Quadrature encoder pulses (QEP), decoded timer clock and direction                                                                                   |            |

| signal                                                                                                                                                           | 249        |

| Figure 8.19 Incremental shaft encoder interface circuit QEP                                                                                                      | 251        |

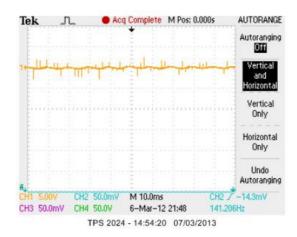

|                                                                                                                                                                  |            |

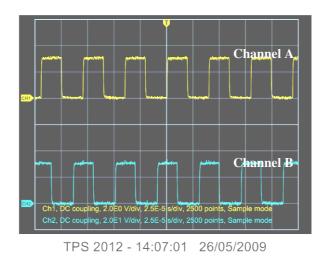

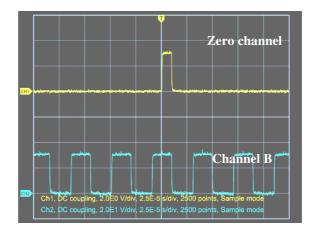

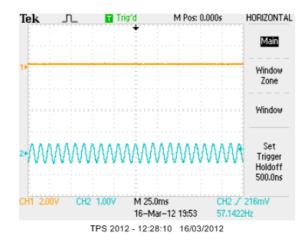

| Figure 8.20 Incremental shaft encoder pulses: bottom plot is the output of the shaft                                                                             |            |

| Figure 8.20 Incremental shaft encoder pulses: bottom plot is the output of the shaft encoder channel A; the top plot is the output of the interface PCB          | 252        |

|                                                                                                                                                                  | 252        |

| encoder channel A; the top plot is the output of the interface PCB                                                                                               |            |

| encoder channel A; the top plot is the output of the interface PCB<br>Figure 8.21 Incremental shaft encoder pulses: channel A is top and channel B is            | 252        |

| encoder channel A; the top plot is the output of the interface PCB<br>Figure 8.21 Incremental shaft encoder pulses: channel A is top and channel B is<br>bottom. | 252<br>253 |

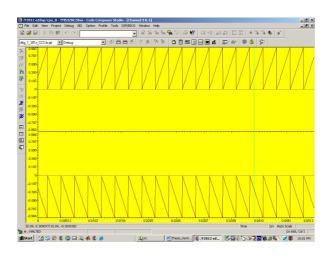

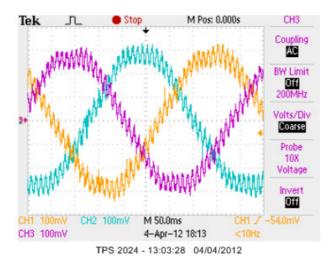

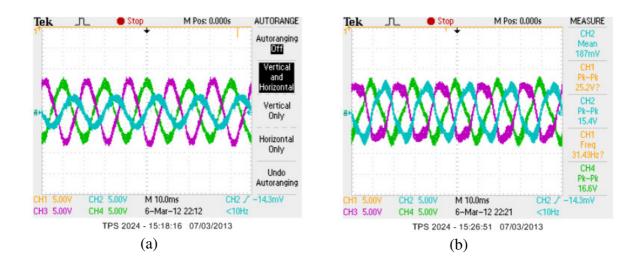

| <i>Figure 8.25 Positive sequence grid voltage angle</i> $\theta_e^+$ (top trace) and negative s                | equence         |

|----------------------------------------------------------------------------------------------------------------|-----------------|

| grid voltage angle $\theta_e^-$ (bottom trace)                                                                 | 255             |

| Figure 8.26 Grid voltage angle $\theta_e$ (Top) and double frequency grid voltage ang                          | le $2x\theta_e$ |

| (Bottom)                                                                                                       | 255             |

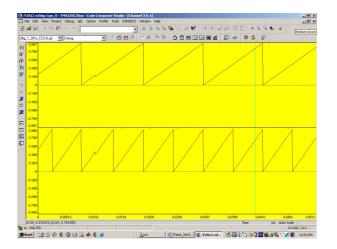

| Figure 8.27 PLL output (Blue Trace) and $\theta_{slip}$ (Yellow Trace) at a speed of 146                       | 2               |

| rev/min.                                                                                                       | 256             |

| Figure 8.28 PLL output and $\theta_{slip}$ at a speed of 710 rev/min.                                          | 256             |

| Figure 8.29 Grid-side converter schematic when network supply is unbalanced                                    | 259             |

| Figure 8.30 DSP ADC Configuration                                                                              | 262             |

| Figure 8.31 Analogue to Digital Converter Software Block                                                       | 262             |

| Figure 8.32 Program structure                                                                                  | 263             |

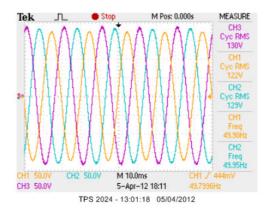

| Figure 9.1 DFIG Interfacing                                                                                    | 264             |

| Figure 9.2 Rotor side converter                                                                                | 266             |

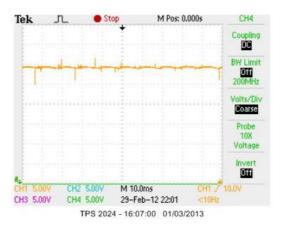

| Figure 9.3 Stator phase voltages - 5% VUF                                                                      | 267             |

| Figure 9.4 Stator positive sequence voltages $V_{ds}^{+}$ (top trace) and $V_{qs}^{+}$ (bottom t               | race). (a)      |

| Balanced stator voltage (b) Stator VUF 5%.                                                                     | 268             |

| Figure 9.5 Stator negative sequence voltages $V_{ds}$ (top trace) and $V_{qs}$ (bottom tr                      | cace) in        |

| negative sequence reference frame                                                                              | 268             |

| Figure 9.6 Stator positive sequence voltage $v_{qs}^+$ (orange trace) and negative sequence voltage $v_{qs}^+$ | quence          |

| voltage $v_{qs}$ (blue trace)                                                                                  | 269             |

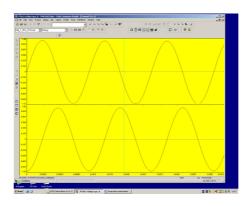

| Figure 9.7 Rotor currents $i_{ra}$ , $i_{rb}$ and $i_{rc}$                                                     | 270             |

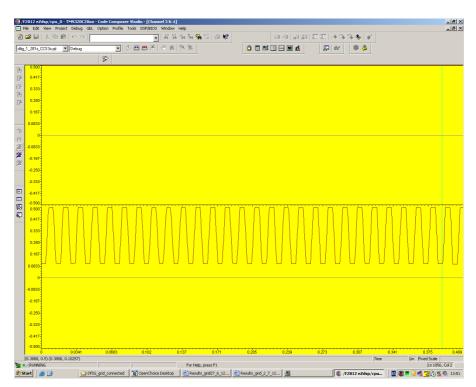

| Figure 9.8 Rotor currents $i_{dr}$ , (top) and $i_{qr}$ (bottom)                                               | 270             |

| Figure 9.9 PIR reference, (Top Plot, just visible at a constant 0.5) and PIR outp                              | out signal      |

| (Bottom Plot)                                                                                                  | 271             |

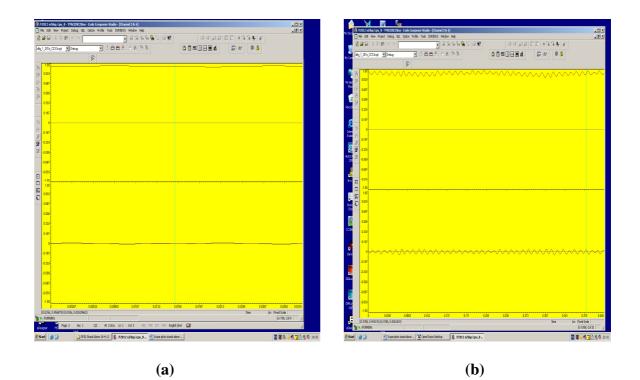

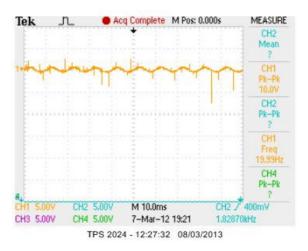

J Kearney PhD Thesis

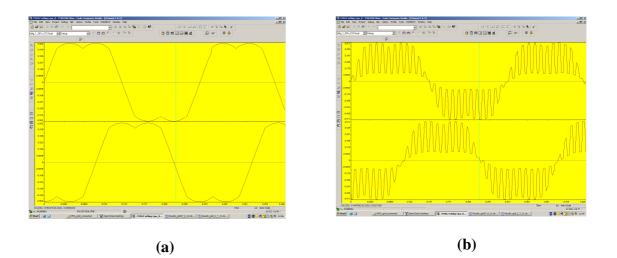

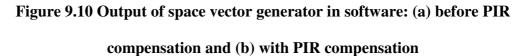

| Figure 9.10 Output of space vector generator in software: (a) before PIR compens                | ation  |

|-------------------------------------------------------------------------------------------------|--------|

| and (b) with PIR compensation                                                                   | _ 272  |

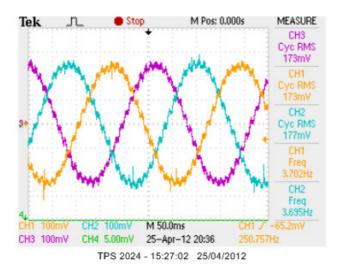

| Figure 9.11 Rotor currents $I_{ra}$ , $I_{rb}$ and $I_{rc}$ with negative sequence compensation | 273    |

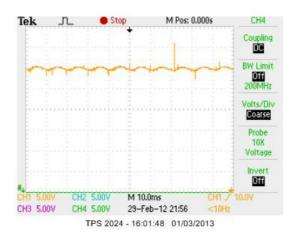

| Figure 9.12 DC Link Voltage, 50V, VUF 5%                                                        | 274    |

| Figure 9.13 DC Link Voltage- 50V -VUF 5%. Compensation Implemented.                             | 275    |

| Figure 9.14 DC link voltage- 50V -VUF 5%                                                        | 275    |

| Figure 9.15 DC link voltage- 50V -VUF 5%. PIR compensation implemented                          | _ 276  |

| Figure 9.16 Grid converter input currents VUF 6%. (a) No negative sequence                      |        |

| compensation (b) PIR compensation implemented                                                   | 277    |

| Figure 9.17 Rotor Currents – Stator VUF 5%: (a) Rotor currents before compense                  | ition. |

| (b) Torque pulsation PIR compensation scheme implemented.                                       | 278    |

| Figure A.1 Laboratory machine set: DC machine and induction Generator                           | _ 303  |

| Figure A.2 Laboratory test rig electrical panel                                                 | _ 303  |

| Figure B1 Schematic diagram of DFIG wiring.                                                     | 304    |

| Figure C.1 Laboratory LEM LA 55P Current Transducer Data Sheet                                  | _ 306  |

| Figure C.2 Laboratory LV 25P Voltage Transducer Data Sheet                                      | 307    |

| Figure D.1 Level shifting circuit                                                               | 308    |

| Figure D.1 Hengstler incremental shaft encoder data sheet                                       | _ 308  |

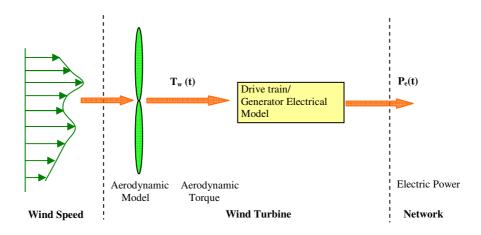

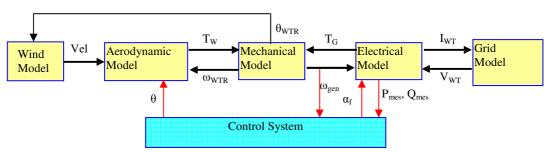

| Figure E.1 Structure of grid-connected wind-turbine model                                       | _ 309  |

| Figure E.2 Overall structure of the grid-connected wind turbine model.                          | _ 309  |

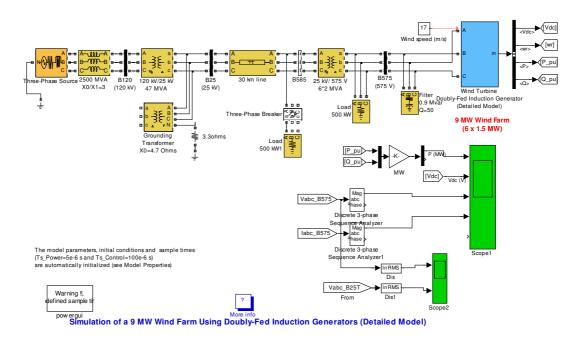

| Figure E.3 An outline of the Matlab/Simulink DFIG wind-farm model                               | _ 310  |

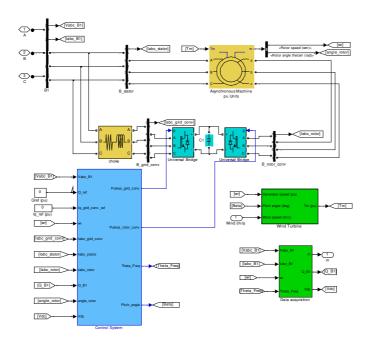

| Figure E.4 An outline of the wind turbine model (shaded blue in Figure A.D.3) $_{-}$            | _ 310  |

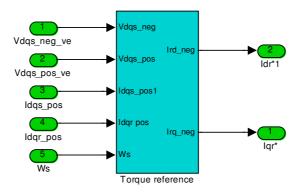

| Figure E.5 Compensation Block                                                                   | 311    |

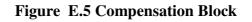

| Figure E.7 Parallel Control Scheme                                                              | _ 311  |

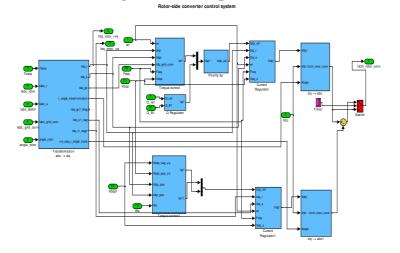

| Figure E.6 Inside Compensation Block                                                            | 312    |

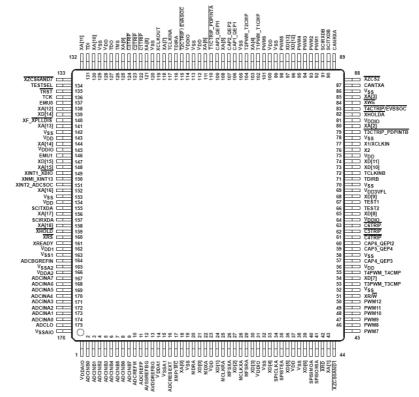

| Figure F.1 TMS320F2812 Pin-out                                                      | 313 |

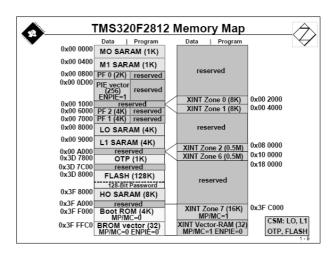

|-------------------------------------------------------------------------------------|-----|

| Figure F.2 TMS320F2812 Memory Map                                                   | 313 |

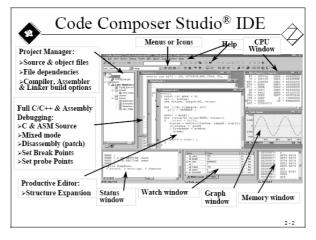

| Figure G.1 Code Composer Studio CCS                                                 | 314 |

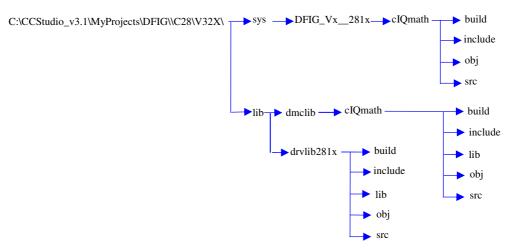

| Figure G.2 File Locations                                                           | 314 |

| Figure G.2 Rotor side converter software modules                                    | 317 |

| Figure G.3 Grid side converter software modules                                     | 318 |

| Figure H 1 Semikron IGBT data sheet                                                 | 322 |

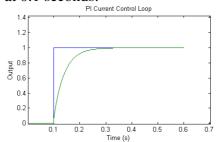

| Figure I 1 PI Step Response Rotor Side Current Loop, Lab machine parameters         | 323 |

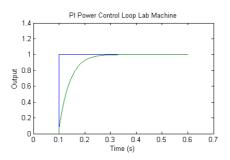

| Figure I 2 PI Step Response Rotor Side Power Control Loop, Lab machine paramet      | ers |

|                                                                                     | 323 |

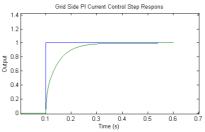

| Figure I 1 PI step response grid side current control loop, lab machine parameters  | 323 |

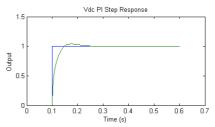

| Figure I 1 PI step response grid side $V_{dc}$ control loop, lab machine parameters | 323 |

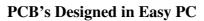

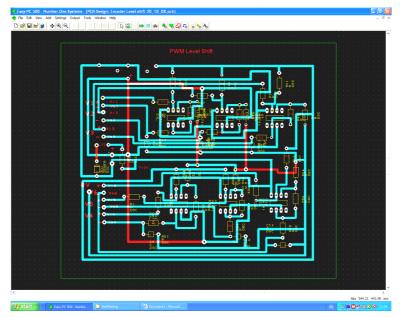

| Figure J1 PWM level shift                                                           | 324 |

| Figure J2 Analogue card - filtering and level shift                                 | 324 |

| Figure J4 PCB Analogue Cards                                                        | 324 |

### List of Tables

| Table 1 Voltage unbalance effects in motors                          |                |

|----------------------------------------------------------------------|----------------|

| Table 2 Power flow direction in DFIG                                 | 64             |

| Table 3 Possible combinations of Stall/Pitch and speed of WECS       | 67             |

| Table 4 Voltage dip classification                                   |                |

| Table 5 Converter gains                                              |                |

| Table 6 Base values                                                  |                |

| Table 7 LEM   LA 55P measurements                                    | 234            |

| Table 8 LEM LV 25P/PCB measurements                                  |                |

| Table 9 LEM LV 25P output (DC Link)                                  | 238            |

| Table 10 Input ADC connections to DSP                                |                |

| Table 11 Encoder and PWM connections to DSP                          |                |

| Table 12 Appendix DC shunt machine                                   |                |

| Table 13 Appendix A induction machine                                |                |

| Table 14 Impedance Parameters of Equivalent Circuit                  |                |

| Table 15 Base Impedance Values                                       |                |

| Table 16 Appendix C - LEM LA 55 P characteristics                    |                |

| Table 17 Main*.C files                                               |                |

| Table 18 Include *.h files                                           |                |

| Table 19 QEP_Theta_DRV                                               |                |

| Table 20 Library files                                               |                |

| Table 21 I/o variable names and corresponding formats for main softw | are modules316 |

| Table 22 DFIG Selection of Control Software Modules                  |                |

| Table 23   Semikron IGBT                                             |                |

# **General conventions**

### The following subscripts are frequently used:

| Maximum value for the considered variable   |

|---------------------------------------------|

| Minimum value for the considered variable   |

| Reference value for the considered variable |

| Error value for the considered variable     |

| Rated value for the considered variable     |

| Base value for the considered variable      |

| Average value of the considered variable    |

| Rotor; rotor reference frame                |

| Stator; stationary reference frame          |

| Synchronous reference frame                 |

| Positive component                          |

| Negative component                          |

| Positive sequence reference frame           |

|                                             |

<sup>-</sup> Negative sequence reference frame

The following operators are frequently used:

- \* complex conjugate;

- absolute value of complex (phasor) variable.

# List of symbols

| В                          | [Tesla]            | ] - | Magnetic flux density                                                                          |

|----------------------------|--------------------|-----|------------------------------------------------------------------------------------------------|

| $C_p$                      | [-]                | -   | Power coefficient                                                                              |

| $C_{dc}$                   | [-]                | -   | DC link capacitance                                                                            |

| $F_s$                      | [Hz]               | -   | Rated stator frequency                                                                         |

| $F_r$                      | [Hz]               | -   | Rotor frequency                                                                                |

| $f_{sw}$                   | [Hz]               | -   | Switching frequency                                                                            |

| Η                          | [A/m]              | -   | Magnetic field strength                                                                        |

| Icrow                      | [A]                | -   | Current flowing via crowbar resistor                                                           |

| $i_{dcg}$                  | [A]                | -   | DC current flowing between DC link and grid side converter                                     |

| <b>i</b> dcr               | [A]                | -   | DC current flowing between DC link and rotor-side converter                                    |

| $i_s$                      | [A]                | -   | Space vector of the stator current                                                             |

| <i>i</i> <sub>r</sub>      | [A]                | -   | Space vector of the rotor current                                                              |

| $i_m$                      | [A]                | -   | Space vector magnetizing current                                                               |

| $i_{lpha s}$ , $i_{eta s}$ | [A]                | -   | Sator $\alpha$ , $\beta$ axis currents                                                         |

| $i_{lpha r}$ , $i_{eta r}$ | [A]                | -   | Stator $\alpha$ , $\beta$ axis currents                                                        |

| $i_{dr}, i_{qr}$           | [A]                | -   | Rotor-side converter current components in the two-axis $(d,q)$<br>Rotational reference frame  |

| $i_{ds}, i_{qs}$           | [A]                | -   | Stator-side converter current components in the two-axis $(d,q)$<br>Rotational reference frame |

| $I_{ag}, I_{bg}$           | , $I_{cg}[A]$      | -   | Grid-side converter ac currents                                                                |

| $i_{lpha s}$ , $i_{eta s}$ | [A]                | -   | stator $\alpha$ , $\beta$ axis currents                                                        |

| $I_s$                      | [A]                | -   | Stator current phasor;                                                                         |

| $I_r$                      | [A]                | -   | Rotor current phasor;                                                                          |

| $J_{gen}[kg$               | g m <sup>2</sup> ] | -   | Induction generator moment of inertia                                                          |

| $J_{ m dc}$                | [A]                | -   | DC machine moment of inertia                                                                   |

| Kgear                      | [-]                | -   | Gearbox ratio                                                                                  |

| $K_{P}$                    | [-]                | -   | Proportional gain                                                                              |

| Kı                         | [-]                | -   | Integral gain                                                                                  |

| Ls, Lr,                    | $L_m$ [H]          | -   | Stator and rotor self-inductances and magnetizing inductance                                   |

| $L_r$ '                    | [H]                | -   | Rotor inductance (referred to stator quantities)                                               |

| L so , I                   | L 15 [H]           | -   | Stator and rotor leakage inductance                                                            |

| Ν                          | [-]                | -   | Number of turns of the induction machine                                                       |

| 3.7                        | r 7                       |   |                                                    |

|----------------------------|---------------------------|---|----------------------------------------------------|

| $N_g$                      | [-]                       | - | Generator nominal speed                            |

| $N_s$                      | [-]                       | - | Number of stator windings;                         |

| $N_r$                      | [-]                       | - | Number of rotor windings;                          |

| р                          | [-]                       | - | Number of pole pairs                               |

| $P_{ m grid}$              | [W]                       | - | Grid-side converter active power                   |

| Protor                     | [W]                       | - | Rotor-side converter active power                  |

| $P_s$                      | [W]                       | - | Stator active power                                |

| $pf_{-ref}$                | [W]                       | - | Reference power factor                             |

| $P_{\mathrm{mech}}$        | [W]                       | - | Mechanical power                                   |

| $P_{\scriptscriptstyle N}$ | [W]                       | - | Rated power of induction generator                 |

| R                          | [Ω]                       | - | Blade radius                                       |

| <b>R</b> crow              | [Ω]                       | - | Crowbar resistor                                   |

| <b>R</b> s, <b>R</b> r     | [Ω]                       | - | Stator and rotor resistances of the phase windings |

| $R_r$ '                    | [Ω]                       | - | Rotor resistance (referred to stator quantities);  |

| Rg                         | [Ω]                       | - | Grid-side converter line filter resistance         |

| $L_{g}$                    | [H]                       | - | Grid-side converter line filter reactance          |

| $Q_{ m grid}$              | [VAr]                     | - | Grid-side converter reactive power                 |

| Qref                       | [VAr]                     | - | Desired reactive power                             |

| $Q_s$                      | [VAr]                     | - | Stator reactive power                              |

| S                          | [pu]                      | - | Generator slip                                     |

| S                          | [pu]                      | - | Apparent power                                     |

| $S_a, S_b,$                | <i>S</i> <sub>c</sub> [-] | - | Switching state of the converter                   |

| $T_e$                      | [Nm]                      | - | Induction generator electromagnetic torque         |

| Te_ref                     | [Nm]                      | - | Reference electromagnetic torque                   |

| $T_{\rm L}$                | [Nm]                      | - | Load torque                                        |

|                            |                           |   |                                                    |

| Tshaft [Nm] -                               | Mechanical torque of the shaft system                                       |

|---------------------------------------------|-----------------------------------------------------------------------------|

| $T_I$ [S]                                   | Integral time of PI controller                                              |

| Vcrow [V] -                                 | Voltage over the crowbar resistor                                           |

| <i>V</i> s [V] -                            | Generator stator voltage                                                    |

| Vr [V] -                                    | Generator rotor voltage                                                     |

| V <sub>max,r</sub> [V] -                    | Generator maximum rotor voltage                                             |

| V <sub>ph</sub> [V] -                       | Phase voltage                                                               |

| <i>V</i> dc [V] -                           | DC link voltage                                                             |

| $V_{ag}, V_{bg}, V_{cg}$ [V] -              | Grid-side converter ac voltages                                             |

| $v_{\alpha s}, v_{\beta s} \left[V ight]$ - | Stator $\alpha$ , $\beta$ axis voltages                                     |

| $v_s, v_r$ [V] -                            | Pace vectors of stator and rotor voltage                                    |

| <i>v<sub>ds</sub></i> [V] -                 | Stator voltage, <i>d</i> -component in $(d,q)$ -reference frame [per unit]; |

| <i>v</i> <sub>qs</sub> [V] -                | Stator voltage, $q$ -component in $(d,q)$ -reference frame [per unit];      |

| <i>v<sub>dr</sub></i> [V] -                 | Rotor voltage, <i>d</i> -component in $(d,q)$ -reference frame [per unit];  |

| <i>v</i> <sub>qr</sub> [V] -                | Rotor voltage, $q$ -component in $(d,q)$ -reference frame [per unit];       |

| $v_{\infty}$ [m/s] -                        | Wind speed                                                                  |

| $X_r$ ' [ $\Omega$ ] -                      | Rotor reactance (referred to stator quantities)                             |

| $X_s$ [ $\Omega$ ] -                        | Stator reactance                                                            |

| $x_{dm}$ [ $\Omega$ ] -                     | Generator magnetising reactance, $d$ -component in $(d,q)$ -reference       |

|                                             | frame                                                                       |

| $x_{qm}$ [ $\Omega$ ] -                     | Generator mutual reactance, $q$ -component in $(d,q)$ -reference frame      |

| $x_{dr}$ [ $\Omega$ ] -                     | Generator rotor reactance, $d$ -component in $(d,q)$ -reference frame       |

| $x_{qr}$ [ $\Omega$ ] -                     | Generator rotor reactance, $q$ -component in $(d,q)$ -reference frame       |

| $x_{ds}$ [ $\Omega$ ] -                     | Generator stator reactance, $d$ -component in $(d,q)$ -reference frame      |

| $x_{qs}$ [ $\Omega$ ] -                     | Generator stator reactance, $q$ -component in $(d,q)$ -reference frame      |

|                                             |                                                                             |

| ψ [pu] -                                 | Flux linkage                                                           |

|------------------------------------------|------------------------------------------------------------------------|

| $\psi_s, \psi_r$ [pu] -                  | Space vectors of the stator and rotor flux linkages                    |

| $\psi_{ds}, \psi_{qs} [pu]$ -            | Generator stator direct and quadrature flux linkages $(d,q)$ -         |

|                                          | reference frame                                                        |

| $\psi_{dr}, \psi_{qr} [pu]$ -            | Generator rotor direct and quadrature flux linkages $(d,q)$ -reference |

|                                          | frame                                                                  |

| $\psi_{\alpha s}, \psi_{\beta s}$ [pu] - | Stationary $\alpha$ , $\beta$ axis stator flux                         |

| $v_{\alpha s}, v_{\beta s}, [V]$ -       | Stationary dq-axis voltages                                            |

| λ [-] -                                  | Tip speed ratio (propeller tip speed divided by wind speed)            |

| heta [deg] -                             | Pitch angle of Blades                                                  |

| $\theta_r$ [deg] -                       | Generator rotor shaft position                                         |

| $	heta_{ m e}$ [deg] -                   | Park's angle (angle of rotational transformation between reference     |

|                                          | frames in DFIG control - synchronous reference frame)                  |

| ho [kg/m³] -                             | Air density                                                            |

| $\omega_e$ [rad/sec] -                   | Synchronous angular velocity of voltage                                |

| $\omega_r$ [rad/sec] -                   | Mechanical angular speed of the rotor shaft                            |

| $\omega_{sl}$ [rad/sec] -                | Induction machine slip speed                                           |

| σ [-] -                                  | Stator and rotor reactance leakage factor                              |

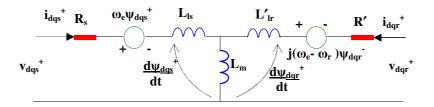

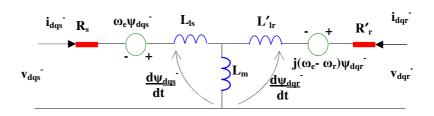

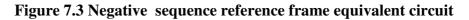

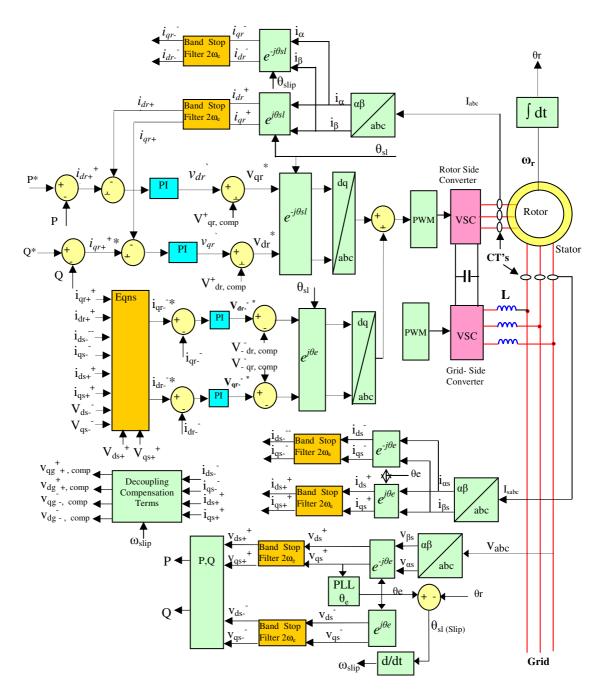

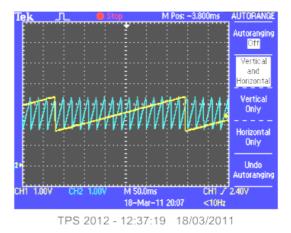

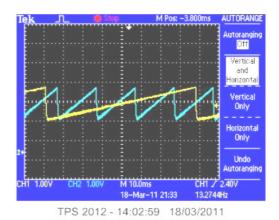

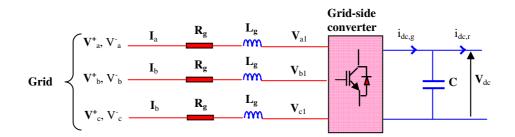

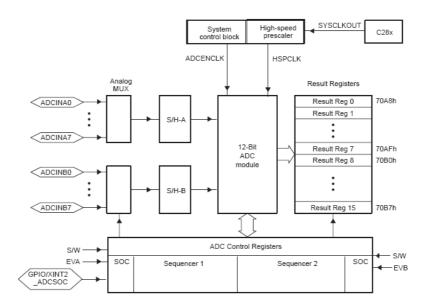

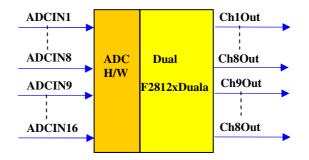

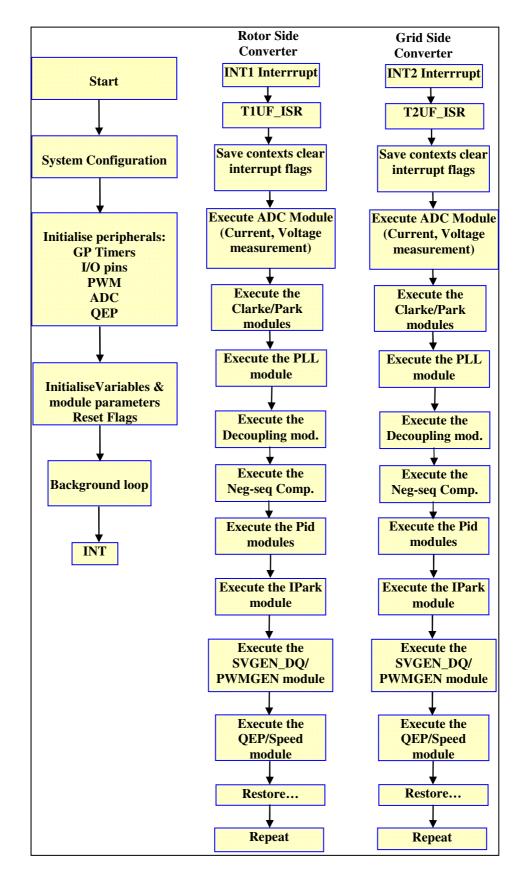

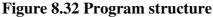

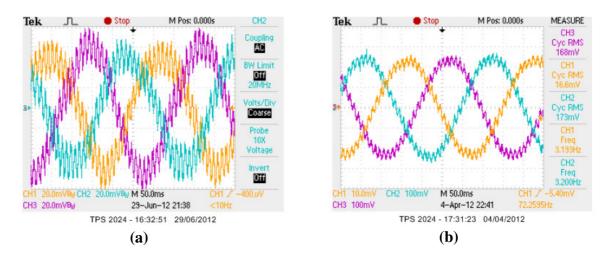

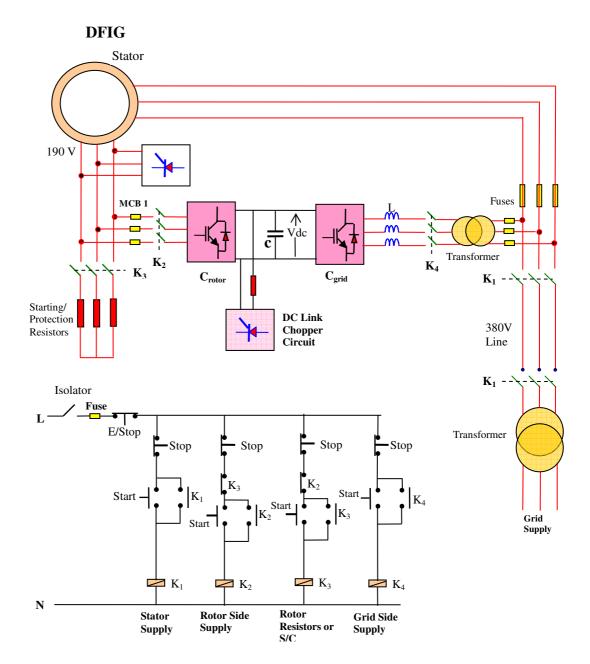

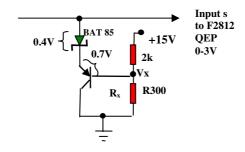

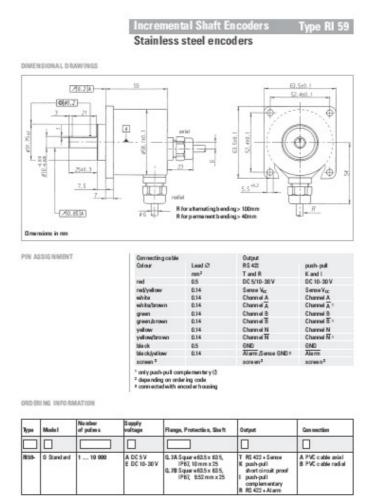

| <i>r</i> <sub>s</sub> [s] -              | Simulink discrete time step                                            |