Technological University Dublin ARROW@TU Dublin

Articles

School of Electrical and Electronic Engineering

2010-06-01

# Development of a 12 kVA DSP-Controlled Laboratory Prototype UPQC

Iurie Axente University of Western Ontario, iaxente@yahoo.com

Jayanti Navilgone Ganesh Technological University Dublin, jayanti\_ng@yahoo.com

Malabika Basu Technological University Dublin, mbasu@tudublin.ie

See next page for additional authors

Follow this and additional works at: https://arrow.tudublin.ie/engscheleart2

Part of the Power and Energy Commons

### **Recommended Citation**

Axente, I., Ganesh, J., Basu, M., Gaughan, K., Conlon, M.: Development of a 12 kVA DSP-Controlled Laboratory Prototype UPQC. IEEE Transactions Power Electronics, Vol. 25(6), pp. 1471-1479. June, 2010. doi:10.1109/TPEL.2010.2040635

This Article is brought to you for free and open access by the School of Electrical and Electronic Engineering at ARROW@TU Dublin. It has been accepted for inclusion in Articles by an authorized administrator of ARROW@TU Dublin. For more information, please contact arrow.admin@tudublin.ie, aisling.coyne@tudublin.ie, vera.kilshaw@tudublin.ie.

## Authors

lurie Axente, Jayanti Navilgone Ganesh, Malabika Basu, Michael Conlon, and Kevin Gaughan

This article is available at ARROW@TU Dublin: https://arrow.tudublin.ie/engscheleart2/6

# A 12-kVA DSP-Controlled Laboratory Prototype UPQC Capable of Mitigating Unbalance in Source Voltage and Load Current

Iurie Axente, Jayanti Navilgone Ganesh, Malabika Basu, Member, IEEE, Michael F. Conlon, Member, IEEE, and Kevin Gaughan

Abstract—This paper reports the development of a laboratory prototype of a fully digital DSP-controlled 12-kVA unified power quality conditioner (UPQC), capable of compensating for both the supply voltage and the load current imperfections. A fully digital controller based on the TMS320F2812 DSP platform is implemented for the reference generation as well as control purposes. The delay problem in the digital controller is overcome by application of a fast DSP, a compact control technique and proper flow of control steps in the DSP software. A phase-locked loopless software grid synchronization method has been implemented for the effective operation of the UPQC under conditions of grid frequency variation. A sequence-based compensation strategy has been developed to compensate for balanced and unbalanced sags while accommodating the fact that the voltage injection capability of the UPQC is limited. The prototype UPQC power circuit, control features, and control algorithm along with experimental results are presented in this paper.

*Index Terms*—Current unbalance and nonlinear load, DSPbased control, power quality conditioning (PQC), unbalanced voltage sag, unified power quality conditioner (UPQC).

#### I. INTRODUCTION

T HE PROLIFERATION of power electronics-based equipment has produced a significant impact on the quality of electric power supply. Nowadays, much of the equipment is based on power electronic devices, often leading to problems of power quality (PQ) [1]. At the same time, this equipment is typically equipped with microprocessor-based controllers, which are quite sensitive to deviations from the ideal sinusoidal line voltage. In such conditions, both electric utilities and end users of electric power are increasingly concerned about the quality of electric power. Conventional PQ mitigation equipment is proving to be inadequate for an increasing number of applications, and this fact has attracted the attention of power engineers to develop dynamic and adjustable solutions to power quality

Manuscript received September 15, 2009; revised December 12, 2009. Current version published June 3, 2010. This work was supported by the Unified Power Quality Conditioner project of the Enterprise Ireland. Recommended for publication by Associate Editor J. J. H. Enslin.

I. Axente is with the Department of Electrical and Computer Engineering, University of Western Ontario, London, ON N6A 5B9, Canada (e-mail: iaxente@uwo.ca; iaxente@yahoo.com).

J. N. Ganesh, M. Basu, M. F. Conlon, and K. Gaughan are with the School of Electrical Engineering Systems, Dublin Institute of Technology, Dublin 8, Ireland (e-mail: jayanti\_ng@yahoo.com; mbasu@dit.ie; mbasu@ieee.org; michael.conlon@dit.ie; kevin.gaughan@dit.ie).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2010.2040635

problems. Thus, between the different technical options available to improve PQ, active power filters (APFs) have proved to be an important alternative to minimize the financial impacts of PQ problems [2], [20]–[26]. One modern and very promising solution is the unified power quality conditioner (UPQC)—a power conditioning device that consists of two APFs connected back-to-back on the dc side and deals with both load current and supply voltage imperfections [3], [4].

Although the APFs have higher cost and complex control, they are much superior in filtering performance than the passive filters. Therefore, APFs are preferred over passive filters as the solution to various PQ problems arising from the load or the supply side. Few obvious reasons for this are [2], [20] described in the following.

- 1) Design of the active filters is almost independent of power system parameters.

- 2) No lengthy tuning effort is required in the design of active filters, which is usual in the case of passive filters.

- Possibility of resonance is excluded in the active filter application.

In [4] and [5], various configurations of APFs are reported. The application of DSP in control of APFs is reported in [6]-[11]. The reference generation and tracking are two identified tasks under any type of control. In [6], DSP is applied to generate the reference source current based on measurement of the source voltage and dc-link voltage. A fully digital controller is implemented in [7]. An attempt has been made to damp the propagation of voltage harmonics in the distribution line. It applies a synchronous rotating frame technique to generate the compensator reference current, and hence, the compensator voltage. Sine pulsewidth modulation (PWM) technique is used to generate the switching for the voltage source inverter (VSI). In [8], the source current reference is generated as an in-phase component of the fundamental positive sequence component of the source voltage, calculated by applying synchronous reference frame transformations. However, in order to avoid the inherent delay introduced by a digital current controller, an analog hysteresis controller is applied to generate switching pulses based on source current reference and measured source current. In [9], four different control techniques of a shunt active power filter are compared at a lower switching frequency of the voltage source converter. In [10], a controller based on a Lagrange multiplier optimization technique to generate the compensator reference current in DSP has been developed. An external hysteresis current controller is implemented to track the compensator

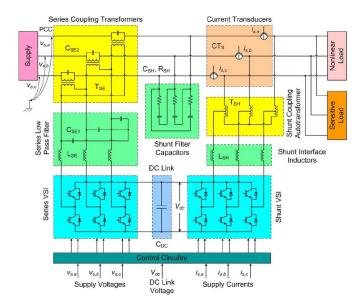

Fig. 1. Power circuit of the prototype UPQC.

reference current. In [11], selective harmonic compensation is implemented to generate the compensator reference current. The delay in the measurement and control action, aliasing effect in digitized voltage and current signals due to switching noise are major concerns in any DSP-based controller. Synchronous sampling and calculation methods are suggested in [7] to eliminate these effects. Additionally, a fast DSP with an A-D converter (ADC) of high conversion rate should be chosen for fast control action. Source current reference generation and control instead of the compensator current is suggested in [8] to avoid the spikes in the source current, when sharp changes occur in nonlinear load current. But delay in the control decision and switching can also cause the source current to go out of bands in the case of hysteresis current control. This remains a problem even if direct source current control is used, but a fast DSP and a compact control technique is not chosen. Fully digital DSP-based series and shunt active power filters have been presented in [12] and [13], respectively.

This paper presents the development of a laboratory prototype of a fully digital DSP-based 12-kVA UPQC, as shown in Fig. 1. A compact digital controller to compensate for both load current imperfections (harmonics, reactive power and unbalance) and supply voltage disturbances (sags, unbalance) is implemented with a ezDSP F2812 development kit (TMS320F2812 32-bit fixed point processor). The controller performs well, both under balance and unbalance supply conditions. A simple software zero-crossing detection-based line frequency synchronizing method has been applied in the control of UPQC. Therefore, a phase-locked loop (PLL)-less control has been achieved, which saves the processor time and does not involve additional hardware. Also, a sequence-based compensation strategy has been developed to compensate for balanced and unbalanced sags considering that the voltage injection capability of the UPQC is limited.

#### II. POWER CIRCUIT

The UPQC is a combination of series and parallel APFs connected back-to-back to a common dc energy storage capacitor [4]. The power circuit layout of the prototype UPQC is shown in Fig. 1. The prototype UPQC is intended to be used in three-phase three-wire systems. The ratings of the prototype UPQC are: 133 (line-neutral)/230 V (line-line) and 17.4 A for the shunt compensator, and 115 V and 34.8 A for the series compensator.

The shunt active filter is responsible for power factor correction and compensation of load current harmonics and unbalances. Also, it maintains constant average voltage across the dc storage capacitor  $C_{\rm dc}$ . The shunt part of the UPQC consists of a VSI connected to the common dc storage capacitor  $C_{\rm dc}$  on the dc side and on the ac side it is connected in parallel with the load through the shunt interface inductors  $L_{\rm SH}$  and a star-connected three-phase shunt coupling auto-transformer  $T_{\rm SH}$ . The shunt interface inductors  $L_{\rm SH}$  are used to filter out the switching frequency harmonics produced by the shunt VSI.  $T_{\rm SH}$  is used for matching the network and VSI voltages.

The series active filter is responsible for voltage compensation during supply side disturbances, such as voltage sag and unbalance. The series part of the UPQC also consists of a VSI connected on the dc side to the same energy storage capacitor  $C_{\rm dc}$ , and on the ac side it is connected in series with the feeder, through the series low-pass filter (LPF) and three individual single-phase series coupling transformers  $T_{\rm SE}$ . The series LPF prevents the switching frequency harmonics produced by the series VSI entering the distribution system.  $T_{\rm SE}$  provide voltage matching and isolation between the distribution network and the series VSI.

The series and shunt inverters are standard six-switch VSIs based on *TOSHIBA MG150J2YS50* IGBT devices (150 A, 600 V). Across the dc link, a 2200  $\mu$ F, 500 V electrolytic capacitor is connected ( $C_{dc}$ ). The initial values of the dc-link capacitor ratings have been estimated based on the recommendations presented in [1, p. 1084 and pp. 1087–1088], [14], [16], [17], and [18, Section 25.2.3.3]. Then, these values have been refined through simulations and experimentally validated. The selection of the shunt coupling inductors, and series LPF has been performed in the same way.

The parameters of the series and shunt coupling transformers are given in Table I.

In order to remove the triplen harmonics in the voltages injected by the series transformers  $T_{\rm SE}$ , caused by the transformer core nonlinearity, the secondary windings of the series transformers are connected in delta. Also, the delta connection of the inverter-side windings maximizes the utilization of the dc-link voltage.

The filter inductors of both shunt and series compensators ( $L_{\rm SH}$  and  $L_{\rm SE}$ , respectively) have the following parameters: L = 1.245 mH and  $R = 0.1 \Omega$ .

The filter capacitors  $C_{\rm SE1}$  connected in star on the secondary side of the series transformers are of 10  $\mu$ F, and those connected across the primary of the series transformer  $C_{\rm SE2}$  are of 300  $\mu$ F

| Parameters                      | Series<br>transf. | Shunt<br>auto-<br>transf. |

|---------------------------------|-------------------|---------------------------|

| Number of phases                | 1-phase           | 3-phase                   |

| Power, kVA                      | 4                 | 12                        |

| Voltages (primary/secondary), V | 115/130           | 230/130                   |

| Core Resistance, $\Omega$       | 363.7             | 1547.3                    |

| Core inductance, mH             | 945               | 10441                     |

| Winding resistance, $\Omega$    | 0.1322            | 0.1588                    |

| Winding leakage inductance, mH  | 0.42              | 0.1684                    |

TABLE I TRANSFORMERS PARAMETERS

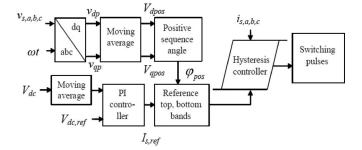

Fig. 2. Control block of the shunt APF.

value. Such level of capacitance is required across the primary of the series transformer to cancel out the low-frequency harmonics, which appear in the injected voltage, mostly due to the blanking time during commutation of the series inverter switches.

The filter capacitors of the shunt compensator  $C_{\rm SH}$  are of 20  $\mu$ F and they are connected in delta. A 4  $\Omega$  damping resistor  $R_{\rm SH}$  is connected in series with each shunt filter capacitor  $C_{\rm SH}$ . This resistor plus proper choice of the shunt inverter switching frequency (hysteresis band) help to avoid resonance at switching frequencies.

#### III. CONTROL SCHEME OF THE UPQC

The DSP implementation of the UPQC control is explained in detail in this section. The choice of DSP kit is very suitable for UPQC control as it contains 16 12-bit ADC channels, 56 general purpose digital ports of which 12 can also act as inbuilt PWM channels, ample on-chip memory as well as external memory, and processing speed of 150 MHz. The parameters of the developed laboratory prototype of the UPQC, control details, and experimental results are presented in the following parts of the paper.

#### A. Control of Shunt Active Power Filter

The shunt active power filter is controlled as a currentcontrolled VSI. The measured source current is controlled to remain within the reference band generated with the help of a hysteresis current controller. The control objective can be explained with the block diagram shown in Fig. 2.

When the UPQC supplies a nonlinear/inductive load, the objective of the shunt converter is to compensate for the load current harmonics, reactive power and unbalance, such that the supply currents are balanced sinusoids (i.e., the distortion is within the limits prescribed by standards) in-phase with the voltages at the point of common coupling (PCC). PCC is the point, where the UPQC is connected to the grid, as shown in Fig. 1. The shunt APF current is controlled indirectly by controlling the source current to be sinusoidal and in-phase with the fundamental positive sequence component of the source voltage. Thus, the system tracks the source current instead of tracking the shunt APF current. Combined with a hysteresis current controller, this control technique involves only the source current measurement. The fundamental positive sequence in-phase and quadrature components of the source voltage and the phase angle are calculated with (1)–(4).

$$\begin{bmatrix} v_{\rm dp} \\ v_{\rm qp} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \sin(\omega t) & \sin(\omega t - 2\pi/3) & \sin(\omega t + 2\pi/3) \\ \cos(\omega t) & \cos(\omega t - 2\pi/3) & \cos(\omega t + 2\pi/3) \end{bmatrix} \times \begin{bmatrix} v_{s,a} \\ v_{s,b} \\ v_{s,c} \end{bmatrix}$$

(1)

$$V_{\rm dpos} = \frac{1}{T} \int_{t-T}^{T} v_{\rm dp} dt$$

(2a)

$$V_{\rm qpos} = \frac{1}{T} \int_{t-T}^{T} v_{\rm qp} dt \tag{2b}$$

$$\varphi_{\rm pos} = \tan^{-1} \left( \frac{V_{\rm qpos}}{V_{\rm dpos}} \right) \tag{3}$$

$$\varphi_{\rm pos} = \tan^{-1} \left( \frac{V_{\rm qpos}}{V_{\rm dpos}} \right) + \pi, \quad \text{if } V_{\rm dpos} < 0 \text{ and } V_{\rm qpos} < 0.$$

(4)

The phase angle  $\varphi_{\rm pos}$  obtained with (1)–(4) is used for calculating the sine template, which is in-phase with the fundamental positive sequence component of the source voltage. The voltage across the dc-link capacitor  $C_{dc}$  is maintained at the reference value 350 V. The dc voltage regulation is achieved by using a proportional and integral (PI) controller. The parameters of the PI controller are:  $K_P = 0.2$  A/V and  $K_I = 2.8$  A/(V · rad). First, these were calculated applying the Ziegler-Nichols tuning rules [19], and then refined through simulations and experimentally validated. The voltage measured across the dc-link capacitor  $C_{dc}$  is compared with the reference value and the voltage error is processed by the PI controller (see Fig. 2). Any variation in the dc-link capacitor voltage is a direct measure of the change in real power requirement of the load. Therefore, the output of the PI controller applied to maintain the dc-link voltage constant is the magnitude of the reference source current, as implemented in [6] and [14]. The current magnitude is multiplied by the sine template to generate the source reference current. A hysteresis band is constructed by adding and subtracting appropriate offset values to the reference. The measured source current is continuously compared against the hysteresis top and bottom bands to generate the switching pulses. More details on the hysteresis

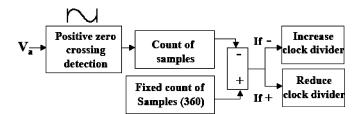

Fig. 3. Frequency locking control block.

controller can be found in [4]. The compactness of the control and flexibility to work under all load current and source voltage circumstances makes it a very attractive choice to implement in a DSP. The current transducers  $CT_S$  for measuring the source currents are installed between the points of connection of the shunt coupling autotransformer  $T_{SH}$  and shunt filter capacitors  $C_{SH}$ , as shown in Fig. 1. Such a connection arrangement is dictated by the use of the hysteresis current controller. If the current transducers  $CT_S$  were installed to the left of the point of connection of the shunt filter capacitors  $C_{SH}$ , the implementation of the hysteresis control strategy would be unsuccessful [15].

The control software is developed in C programming language using code composer studio environment and loaded into DSP. The interrupt service routine (ISR), where switching decisions are made, is operated at around 18 kHz. A frequencylocking algorithm is implemented as shown in Fig. 3.

The program is started with a 50-Hz approximation of the source frequency. For this purpose, the supply voltage is measured and passed through a scaling and filter circuit for proper ADC interface and to eliminate the high frequency noise. The zero crossing of the "A" phase source voltage at negative to positive half-cycle transition is detected with a simple threshold comparison method. A noisy zero crossing is a potential threat for this method of synchronization. To avoid detection of multiple zero crossing, any successive zero crossing detected is discarded for next 30 samples after the first one is detected. The number of samples for one power cycle is counted. This is compared with a fixed number of samples every time the zero crossing is detected (360 samples in this paper, considering 18 kHz as the sampling frequency). If the grid frequency is higher than 50 Hz, a positive difference is calculated. Therefore, the speed of the clock synchronized with the ISR and ADC sampling should be increased to synchronize with the grid frequency. Therefore, the clock dividing register value is reduced to increase ISR and ADC sampling frequency. The clock divider is updated in the other way, if the grid frequency falls below 50 Hz. The clock divider is adjusted gradually in several steps (considering a slow variation of the supply frequency), such that the difference between the sample count and the fixed count reduces to zero. Therefore, the ISR and ADC sampling frequency will be around 18 kHz to take into consideration the supply frequency variations. The register associated with the ISR timer is shadowed in F2812 DSP, which means the register can be updated anywhere in the ISR and can be made effective with different events of the timer (period match and overflow/underflow of counter register). Faulty frequency variation detection is avoided by gradually adjusting the clock divider and by setting upper and lower limits of frequency variation. The details are also provided in [13].

The ADC sampling remains synchronized with the supply frequency, since supply frequency is tracked continuously. The inherent delay caused by the ADC sensing and calculations in the digital hysteresis controller is of great concern, when these types of current controllers are designed. To avoid the delay in switching decisions, the measured source current is compared with the reference value of the current calculated in the previous ISR time. This avoids the delay in switching that can be caused by the calculation time (about 30  $\mu$ s). The switching decision is sent to six inbuilt general-purpose I/O ports.

#### B. Control of the Series Active Power Filter

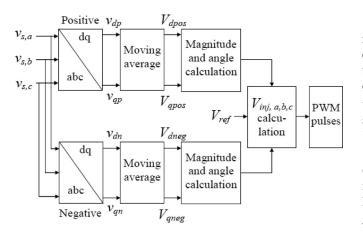

The series active power filter is controlled as a voltagecontrolled VSI. It maintains the load voltage at a predetermined level during source voltage abnormal conditions, such as voltage sag and unbalance. The series APF of the prototype UPQC has restricted voltage injection capability (injection limited to 50% of the supply voltage). The upper limit of injection in any voltage-conditioning device is determined by the rating of the inverter and associated injection transformer. The rating of the inverter and transformer are determined by the requirement to keep the cost of the equipment low. Therefore, it is necessary to take the rating factor of the device into consideration while designing the controller in order to perform optimally with the available rating of the device. A sequence analysis-based compensation strategy has been developed to compensate balanced and/or unbalanced incoming voltage to regulate the load voltage. The advantage of the scheme is that under most of the practical cases of unbalance, the series APF controller is able to fully compensate the unbalance, provided the voltage rating of the series APF is higher than the negative sequence voltage magnitude. This sequence analysis-based control strategy is implemented with a control-optimized fixed-point TI DSP (TMS320F2812) mentioned earlier. A feed-forward control loop measures the source voltage continuously, and it is compared with the reference voltage to be maintained at the load. The voltage to be injected is calculated and the appropriate switching signals are sent to the insulated gate bipolar transistor (IGBT) switches. The inbuilt PWM ports of the DSP provide switching pulses at 18 kHz frequency. The control block is given in Fig. 4.

Three phase voltages are sensed and converted to positive and negative sequence in-phase and quadrature components as shown in (1) and (5).

Then, the fundamental positive and negative sequence components [which are transformed to dc in (1) and (5)] are extracted with the help of a moving average filter (acts as a low-pass filter)

Fig. 4. Control block of series APF.

over a period of one power frequency cycle as shown in (2a), (6a), (2b), and (6b).

$$V_{\rm dneg} = \frac{1}{T} \int_{t-T}^{T} v_{\rm dn} dt \tag{6a}$$

$$V_{\rm qneg} = \frac{1}{T} \int_{t-T}^{T} v_{\rm qn} dt.$$

(6b)

The magnitude and phase angle of the positive and negative sequence components are calculated with (7a) and (7b), and (3) and (8), respectively. When determining  $\varphi_{\text{pos}}$ , if both  $V_{\text{qpos}}$  and  $V_{\text{dpos}}$  are negative values,  $\pi$  should be added to the value obtained with (3). The same rule applies for determining  $\varphi_{\text{neg}}$ . If both  $V_{\text{qneg}}$  and  $V_{\text{dneg}}$  are negative values,  $\pi$  should be added to the value obtained with (8).

$$V_{\rm pos} = \sqrt{V_{\rm dpos}^2 + V_{\rm qpos}^2} \tag{7a}$$

$$V_{\rm neg} = \sqrt{V_{\rm dneg}^2 + V_{\rm qneg}^2} \tag{7b}$$

$$\varphi_{\rm neg} = \tan^{-1} \left( \frac{V_{\rm qneg}}{V_{\rm dneg}} \right).$$

(8)

The series APF control aims to maintain the positive sequence component at a predetermined value, and to reduce the negative sequence and zero-sequence components to zero. In a threephase three-wire system (which is the case in this paper) the zero-sequence component is zero. Therefore, the voltage to be injected in a particular phase is the vector difference of the reference load voltage  $\vec{V}_{ref,k}$ , and positive  $\vec{V}_{pos,k}$  and negative  $\vec{V}_{neg,k}$ sequences of the supply voltage, as shown in (9). The reference load voltage  $\vec{V}_{ref,k}$  is in-phase with the positive sequence of the supply voltage  $\vec{V}_{pos,k}$ . Therefore, in (9), their magnitudes are subtracted from each other.

$$\vec{V}_{\text{inj},k} = V_{\text{inj},k} \angle \varphi_{\text{inj},k} = \vec{V}_{\text{ref},k} - \vec{V}_{\text{pos},k} - \vec{V}_{\text{neg},k}$$

$$= (V_{\text{ref}} - V_{\text{pos}}) \angle (\varphi_{\text{pos}} + \alpha_k) - V_{\text{neg}} \angle (\varphi_{\text{neg}} - \alpha_k)$$

(9)

where k = a, b, c,  $\alpha_a = 0$ ,  $\alpha_b = -2\pi/3$ ,  $\alpha_c = 2\pi/3$ , and  $2\alpha_k = -\alpha_k$ , respectively.

The injected voltage  $\vec{V}_{inj,k}$  is added to the source voltage to regulate the load voltage at the desired level. The voltage that can be injected by the series APF in order to establish a balanced three-phase system on the load side is determined by the rating of its inverter. If the desired magnitude  $V_{inj,k}$  of the injected voltage  $\vec{V}_{inj,k}$  calculated with (9) is beyond the capacity of the series APF, it has to be limited to the maximum voltage capacity  $V_{inj,max}$  of the series APF.

The injected voltage  $V_{\text{inj},k}$  for each phase is calculated with (9). Then, the phase that requires maximum injection is selected, i.e., the phase having the greatest injected voltage magnitude. Let us mark that phase with m (if for example phase c has the greatest injected voltage magnitude, then m = c). The magnitude of the injected voltage for that phase  $V_{\text{inj},m}$  is compared with the maximum possible value  $V_{\text{inj},\text{max}}$ . The following three cases are identified:

- Case 1:  $V_{\text{inj},m} \leq V_{\text{inj},\text{max}}$ . The magnitude of the injected voltages  $V_{\text{inj},k}$  calculated with (9) is within the capacity of the series APF and no further calculation is required. Thus, the series APF injects the voltages calculated with (9). The resulting load voltages are fully balanced and their magnitudes are equal to the reference load voltage  $V_{\text{ref}}$ .

- *Case 2:*  $V_{inj,m} > V_{inj,max}$  and  $V_{neg} \le V_{inj,max}$ . In order to ensure the absolute balancing of the load voltages, the negative sequence component has to be fully compensated, which is possible in this case. Thus, the injected voltage will contain the negative sequence component  $(-V_{neg,k} \measuredangle (\varphi_{neg} \alpha_k))$ . Also, it will contain the positive sequence component, but its magnitude  $(V'_{ref} V_{pos})$  will be lower than the desired one  $(V_{ref} V_{pos})$ , in order to keep the injected voltage magnitude  $V_{inj,m}$  equal to the maximum possible magnitude  $V_{inj,max}$ . This means that the reference load voltage has to be appropriately reduced from the desired value  $V_{ref}$  to a lower value  $V'_{ref}$  such that  $V_{inj,m} = V_{inj,max}$ . Thus, (9) has to be rewritten for phase *m* (phase which requires maximum injection) as shown in (10).

$$\vec{V}_{\text{inj},m} = V_{\text{inj},\max} \angle \varphi_{\text{inj},m} = (V'_{\text{ref}} - V_{\text{pos}}) \angle (\varphi_{\text{pos}} + \alpha_m)

- V_{\text{neg}} \angle (\varphi_{\text{neg}} - \alpha_m).$$

(10)

The new reference load voltage  $V'_{\rm ref}$  is calculated as follows. First, (10) is multiplied by  $1 \angle (-\varphi_{\rm pos} - \alpha_m)$ ; then, the negative sequence component is presented in rectangular form. The result of these transformations is (11) from which (12) is derived. Taking into account that  $2\alpha_m = -\alpha_m$ , appropriate substitution is made in (11) in order to avoid spending the valuable processor time on performing unnecessary mathematical operations.

$$V_{\rm inj,max} \angle (\varphi_{\rm inj,m} - \varphi_{\rm pos} - \alpha_m)$$

=  $V_{\rm ref}' - V_{\rm pos} - V_{\rm neg} \angle (\varphi_{\rm neg} - \varphi_{\rm pos} - 2\alpha_m)$

=  $V_{\rm ref}' - V_{\rm pos} - V_{\rm neg} \angle (\varphi_{\rm neg} - \varphi_{\rm pos} + \alpha_m)$

=  $V_{\rm ref}' - V_{\rm pos} - V_{\rm neg} \cos (\varphi_{\rm neg} - \varphi_{\rm pos} + \alpha_m)$

$- j V_{\rm neg} \sin (\varphi_{\rm neg} - \varphi_{\rm pos} + \alpha_m)$  (11)

$$V_{\rm inj,max}^2 = \left[V_{\rm ref}' - V_{\rm pos} - V_{\rm neg}\cos\left(\varphi_{\rm neg} - \varphi_{\rm pos} + \alpha_m\right)\right]^2 + V_{\rm neg}^2\sin^2\left(\varphi_{\rm neg} - \varphi_{\rm pos} + \alpha_m\right).$$

(12)

Solving (12) for  $V_{\rm ref}^\prime,$  the new reference load voltage  $V_{\rm ref}^\prime$  is obtained, as shown in (13).

$$V'_{\rm ref} = V_{\rm pos} + V_{\rm neg} \cos \left(\varphi_{\rm neg} - \varphi_{\rm pos} + \alpha_m\right) + \sqrt{V_{\rm inj,max}^2 - V_{\rm neg}^2 \sin^2 \left(\varphi_{\rm neg} - \varphi_{\rm pos} + \alpha_m\right)}.$$

(13)

The injected voltages have to be recalculated using (9) in which  $V_{\rm ref}$  is substituted by  $V'_{\rm ref}$ . Thus, the injected voltage is restricted to a combination of negative sequence component and reduced positive sequence component in all phases in order to stay within the limit of the series APF. The resulting load voltages are fully balanced, but their magnitudes are less than the desired value (reference load voltage  $V_{\rm ref}$ ).

Case 3:  $V_{inj,m} > V_{inj,max}$  and  $V_{neg} > V_{inj,max}$ . In this case, in order to balance the load voltage as much as possible, the maximum possible negative sequence voltage is injected, i.e., the injected voltages are recalculated to be  $ec{V}_{ ext{inj},k} = -V_{ ext{inj}, ext{max}} \measuredangle \left( arphi_{ ext{neg}} - lpha_k

ight)$  . This is the case when the absolute balancing of the load voltages cannot be achieved. Thus, in this worst case, the resulting load voltages are not fully balanced and their magnitudes are less than the desired value (reference load voltage  $V_{\rm ref}$ ).

#### C. Control of the Integrated UPQC

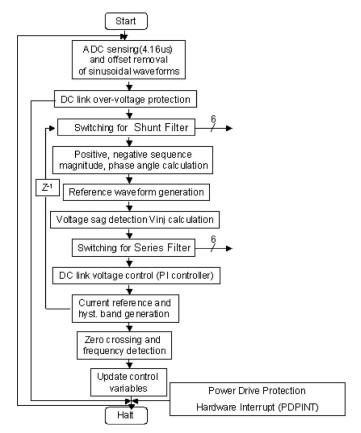

Fig. 5 shows the integrated flowchart for the full digital control and operation of the UPQC that is implemented through the DSP.

From the flowchart it can be seen that the algorithm is integrated with digital protection of dc-link overvoltage, and offsets the measurement errors of the ADCs.

#### **IV. EXPERIMENTAL RESULTS**

#### A. Steady-State Results

The prototype UPQC presented in Section II and Section III is implemented and the following experimental results have been obtained. The nominal supply voltage of the experimental setup is 230 Vrms line-to-line. An ac power source of type 4500Ls produced by California Instruments has been used throughout the experiment.

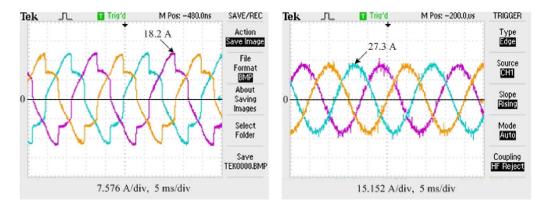

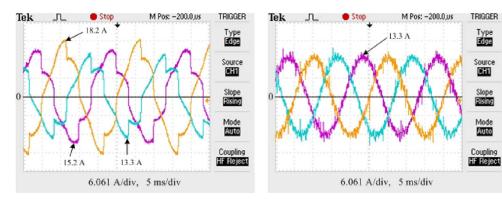

Three loads are connected to the UPQC: resistive, inductive, and nonlinear (resistor connected to a three-phase diode bridge rectifier). The total currents drawn by these three loads are shown in Fig. 6(a), where total harmonic distortion (THD) per phase is 15.8%.

In Fig. 6(b) the supply currents are shown. These are balanced sinusoids containing some admissible ripple (THD = 4.45%, whereas the limit recommended by IEEE Standard 519-1992 is 8%).

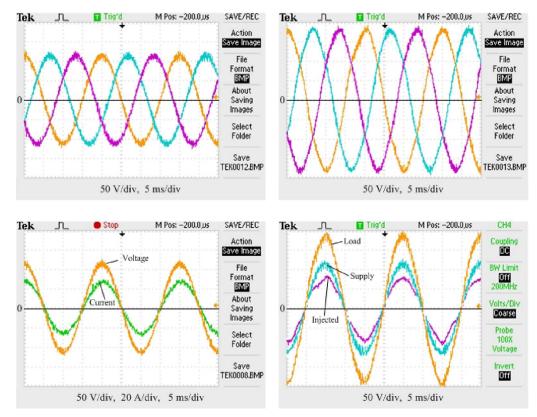

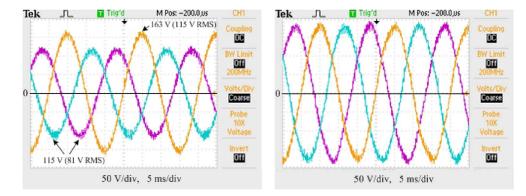

A 40% supply voltage sag has been created. The supply voltages are shown in Fig. 7(a). Due to series injection, the load witnesses the voltages presented in Fig. 7(b), which are balanced sinusoids with the magnitude equal to 188 V peak per phase

Fig. 5. Complete flowchart of UPQC control.

(corresponds to 230 Vrms line-line), as desired. The THDs of both the supply (2.3%) and the load (1.5%) voltages are below the 5% limit, recommended by IEEE Standard 519–1992.

It can be seen in Fig. 7(c) that the supply voltage and current are in-phase, which means that no reactive power is drawn from the supply. The supply, injected, and load voltages are all inphase, as shown in Fig. 7(d).

#### B. Dynamic Condition Results

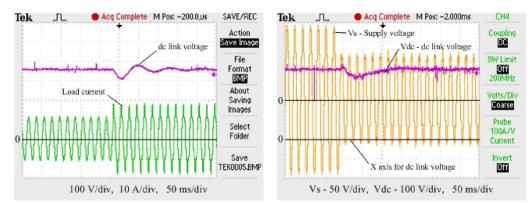

In the steady state, the shunt compensator maintains the dclink voltage constant at 350 V. The dc-link voltage dynamics after connection of the nonlinear load is shown in Fig. 8(a). The dc-link voltage drops down by about 50 V, when the nonlinear load is switched ON. In this case, the dc-link capacitor has to supply the real power to the load until a new supply current reference suitable for new load condition is calculated.

Fig. 8(b) shows another dynamic condition for the dc-link voltage at the occurrence of supply voltage sag (a 40% sag has been created). The sag occurrence results in a sudden increase of the supply current. Before a new supply current reference is determined, the dc-link capacitor is supplying real power to the load causing the dc-link voltage drop (about 50 V). The dc-link voltage is stabilized soon after the controller sets the new supply current reference.

A load unbalance has been created while having normal supply voltages. The load currents are both distorted and unbalanced [see Fig. 9(a)]. However, due to the action of the shunt

- -

Fig. 6. Load currents and supply currents. (a) Load currents (THD = 15.8%). (b) Supply currents (THD = 4.45%).

Fig. 7. Voltages at various points. (a) Supply voltages (THD = 2.3%). (b) Load voltages (THD = 1.5%). (c) Voltage and current of phase *a*. (d) Supply, injected and load, phase *a*.

Fig. 8. Dynamic performance of the dc link of the UPQC at various disturbances. (a) Dynamic performance due to connection of nonlinear load. (b) Dynamic performance at the occurrence of supply voltage sag.

Fig. 9. Load unbalance. (a) Load currents. (b) Supply currents (THD = 4.5%).

Fig. 10. Supply voltage unbalance. (a) Supply voltages (THD = 2.3%). (b) Load voltages (THD = 1.7%).

compensator, the source currents [see Fig. 9(b)] are balanced sinusoids (containing some acceptable ripple, THD = 4.5%).

Also, an unbalanced supply voltage sag has been created as shown in Fig. 10(a), where the supply voltages are unbalanced sinusoids with the magnitudes below the nominal level. Due to appropriate series injection, the load voltages [see Fig. 10(b)] are balanced sinusoids (THD = 1.7%) with magnitudes equal to 188 V peak per phase (corresponding to 230 Vrms, line–line) as specified in the design.

#### V. CONCLUSION

A fully digital controller for a UPQC has been implemented with a DSP. A PLL-less grid synchronization method applicable in a digital controller of the UPQC has been implemented. The delay problem in digital controller has been overcome by the application of a fast DSP, a compact control technique, and proper flow of control steps in the DSP software. A sequence component-based controller has been developed for the series APF, which is simple and elegant to implement with a DSP. The proposed control scheme takes into consideration the injected voltage limitation of the series APF and ensures the unbalance compensation under different unbalance conditions. The advantage of the mitigation scheme is that under most of the practical cases of unbalance, the series APF controller is able to fully compensate the unbalance, provided the voltage rating of the series APF is higher than the negative sequence voltage magnitude. Based on experimental results presented earlier, it can be concluded that the performance of the DSP-based controller proved to be very satisfactory for the steady-state as well as dynamic conditions for the UPQC.

#### REFERENCES

- M. H. Rashid, Power Electronics Handbook: Devices, Circuits, and Applications. New York: Elsevier, 2007.

- [2] H. Akagi, "Trends in active power line conditioners," *IEEE Trans. Power Electron.*, vol. 9, no. 3, pp. 263–268, May 1994.

- [3] H. Fujita and H. Akagi, "The unified power quality conditioner: The integration of series- and shunt-active filters," *IEEE Trans. Power Electron.*, vol. 13, no. 2, pp. 315–322, Mar. 1998.

- [4] A. Ghosh and G. Ledwich, Power Quality Enhancement Using Custom Power Devices. Boston, MA: Kluwer, 2002.

- [5] H. Akagi, "Active harmonic filters," *Proc. IEEE*, vol. 93, no. 12, pp. 2128– 2141, Dec. 2005.

- [6] A. Chandra, B. Singh, B. N. Singh, and K. Al-Haddad, "An improved control algorithm of shunt active filter for voltage regulation, harmonic elimination, power factor correction and balancing of nonlinear loads," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 495–507, May 2000.

- [7] P. Jintakosonwit, H. Fujita, and H. Akagi, "Control and performance of a fully-digital-controlled shunt active filter for installation on a power distribution system," *IEEE Trans. Power Electron.*, vol. 17, no. 1, pp. 132– 140, Jan. 2002.

- [8] G. Bonifacio, A. Lo Schiavo, P. Marino, and A. Testa, "A new DSP controlled shunt active filter for non ideal supply conditions," in *Proc. IEEE 31st Annu. Power Electron. Spec. Conf. (PESC)*, Jun. 2000, pp. 476– 481.

- [9] J. Svensson and R. Ottersten, "Shunt active filter of vector currentcontrolled VSC at a moderate switching frequency," *IEEE Trans. Ind. Appl.*, vol. 35, no. 5, pp. 1083–1090, Sep./Oct. 1999.

- [10] S. George and V. Agarwal, "A DSP based optimal algorithm for shunt active filter under nonsinusoidal supply and unbalance load condition," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 593–601, Mar. 2007.

- [11] L. H. Tey and P. L. So, "DSP-controlled active filters for system harmonics compensation," in *Proc. Int. Conf. Power Syst. Technol.*, Oct. 2002, vol. 1, pp. 453–458.

- [12] N. G. Jayanti, M. Basu, I. Axente, K. Gaughan, and M. F. Conlon, "Sequence analysis based DSP controller for Dynamic Voltage Restorer (DVR)," in *Proc. 39th IEEE Power Electron. Spec. Conf. (PESC)*, Rhodes, Greece, Jun. 15th–19th, 2008, pp. 3986–3991.

- [13] N. G. Jayanti, M. Basu, I. Axente, K. Gaughan, and M. F. Conlon, "Development of laboratory prototype of a 12 kVA digital shunt active filter," in *Proc. 34th IEEE Ind. Electron. Soc. Conf. (IECON)*, 2010, Florida, USA, Nov. 10th–13th, 2008, pp. 3129–3134.

- [14] K. Chatterjee, B. G. Fernandes, and G. K. Dubey, "An instantaneous reactive volt-ampere compensator and harmonic suppressor system," *IEEE Trans. Power Electron.*, vol. 14, no. 2, pp. 381–392, Mar. 1999.

[15] I. Axente, M. Basu, and M. F. Conlon, "A control approach for UPQC

- [15] I. Axente, M. Basu, and M. F. Conlon, "A control approach for UPQC connected to week supply point," in *Proc. 42nd Int. Univ. Power Eng. Conf.* (UPEC), Univ. Brighton, Brighton, UK, Sep. 4th–6th. 2007, pp. 619–623.

- [16] S. K. Jain, P. Agrawal, and H. O. Gupta, "Fuzzy logic controlled shunt active power filter for power quality improvement," *Inst. Electr. Eng. Proc.-Electr. Power Appl.*, vol. 149, no. 5, pp. 317–328, Sep. 2002.

- [17] T. Thomas, K. Haddad, G. Joos, and A. Jaafari, "Design and performance of active power filters," *IEEE Ind. Appl. Mag.*, vol. 4, no. 5, pp. 38–46, Sep./Oct. 1998.

- [18] L. L. Grigsby, *Electric Power Engineering Handbook*, 2nd ed. New York: Taylor & Francis, 2007.

- [19] K. Dutton, S. Thompson, and B. Barraclough, *The Art of Control Engineering*. Harlow, U.K.: Addison-Wesley, 1997.

- [20] H. Akagi, Instantaneous Power Theory and Applications to Power Conditioning. New York: Wiley, 2007.

- [21] M. J. Newman, D. N. Zmood, and D. G. Holmes, "Stationary frame harmonic reference generation for active filter systems," *IEEE Trans. Ind. Appl.*, vol. 38, no. 6, pp. 1591–1599, Nov./Dec. 2002.

- [22] M. J. Newman, D. G. Holmes, J. G. Nielsen, and F. Blaabjerg, "A dynamic voltage restorer (DVR) with selective harmonic compensation at medium voltage level," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1744–1753, Nov./Dec. 2005.

- [23] J. G. Nielsen, M. Newman, H. Nielsen, and F. Blaabjerg, "Control and testing of a dynamic voltage restorer (DVR) at medium voltage level," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 806–813, May 2004.

- [24] J. G. Nielsen and F. Blaabjerg, "A detailed comparison of system topologies for dynamic voltage restorers," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1272–1280, Sep./Oct. 2005.

- [25] S. J. Lee and S. K. Sul, "A harmonic reference frame based current controller for active filter," in *Proc. 15th Annu. IEEE Appl. Power Electron. Conf. Expo. (APEC 2000*, vol. 2, pp. 1073–1078.

- [26] L. Asiminoaei, E. Aeloiza, J. H. Kim, P. Enjeti, F. Blaabjerg, L. T. Moran, and S. K. Sul, "Parallel interleaved inverters for reactive power and harmonic compensation," in *Proc. 37th IEEE Power Electron. Spec. Conf.* (*PESC*), Jun. 18–22, 2006, pp. 1–7.

Jayanti Navilgone Ganesh was born in Karnataka, India, on July 22, 1979. She received the B.E. degree from Bangalore University, Bangalore, India, in 2001, and the Ph.D. degree from Dublin Institute of Technology, Dublin, Ireland, in 2009, both in electrical engineering.

Her research interests include renewable energy, grid integration of renewable energy sources, active filters, custom power devices, flexible ac transmission systems (FACTS) devices, and DSP-based controllers for FACTS and custom power devices.

**Malabika Basu** (S'99–M'03) received the B.E. and M.E. degrees in electrical engineering from Bengal Engineering College, Shibpur, Kolkata, India, in 1995 and 1997, respectively, and the Ph.D. degree in electrical engineering from Indian Institute of Technology, Kanpur, Uttar Pradesh, India, in 2003.

From 2001 to 2003, she was a Lecturer in Jadavpur University, Kolkata, West Bengal, India. From 2003 to 2006, she was Arnold F. Graves Postdoctoral Fellow at Dublin Institute of Technology, Dublin, Ireland, where she has been a Lecturer, since 2006.

She has authored or coauthored more than 40 technical publications in various international journals and conference proceedings. Her current research interests include grid integration of renewable energy sources, power quality conditioners and power quality control and analysis, photovoltaics and wind energy conversion, and smart grid and microgrids.

Michael F. Conlon (M'88) received the Dip.E.E., B.Sc. from Dublin Institute of Technology, Dublin, Ireland, in 1982, the M.Eng.Sc. degree by research and the Ph.D. degree from the University College, Galway, Ireland, in 1984 and 1987, respectively, all in electrical engineering.

He was at Monash University and Victorian Energy Networks Corporation, Melbourne, Vic., Australia. Currently, he is the Head of the Department of Control Engineering at the Dublin Institute of Technology, Dublin, Ireland. His research interests include

power systems analysis and control applications, power systems economics, integration of wind energy in power networks, and quality of supply and reliability assessment.

**Iurie Axente** received the B.Sc. degree from the Technical University of Moldova, Chisinau, Moldova, in 1993, the M.Sc. degree from the Royal Institute of Technology, Stockholm, Sweden, in 2002, and the Ph.D. degree from Dublin Institute of Technology, Dublin, Ireland, in 2008, all in electrical engineering.

From 1993 to 1998, he was a Teaching Assistant and an Assistant Lecturer at the Technical University of Moldova. He was an Utility Regulation Specialist for the Energy Regulatory Agency of Moldova during

1998–2000, and for I.C.S. "RED Union Fenosa" S.A. (an electricity distribution company in Moldova) during 2002–2005. In 2009, he was an Instructor at the Southern Alberta Institute of Technology, Calgary, Canada. He is currently a Postdoctoral Fellow at the University of Western Ontario, London, Canada. His research interests include modeling and design and control of power electronics applications in power systems (flexible ac transmission systems, custom power devices, and interfacing of renewable and distributed generation).

Kevin Gaughan received the B.E. and M.Eng.Sc. degrees from the University College, Galway, Dublin, Ireland, in 1985 and 1987, respectively, both in electrical engineering and the M.B.A. degree from Dublin City University, Dublin, in 1998.

From 1987 to 2002, he worked in power electronic systems design and progressed to technology company management. He was a Lead Designer on a number of innovative projects including the Moog 150A Brushless Motor Controller and the Power Test Loadsaver Energy recycling load. Since 2002, he has

Lectured in electrical engineering at the Dublin Institute of Technology, Dublin, where he is engaged in research in the fields of power electronics, power quality, and electric power systems.